分类号:

TN256

单位代码:

10335

密 级:

无

学 号:

21960356

# 浙江大学

# 硕士专业学位论文

中文论文题目: 低损耗光栅耦合器设计

英文论文题目: Low Loss Grating Coupler Design

| 申请人姓名:  | 維翔宇       |

|---------|-----------|

| 指导导师:   | 储涛        |

| 合作导师:   | 米光灿       |

| 专业学位类别: | :工学       |

| 专业学位领域: | : 集成电路工程  |

| 所在学院:   | 信息与电子工程学院 |

论文提交日期 \_\_2022年03月\_

# 低损耗光栅耦合器设计

论文作者签名: 解翔宇

指导教师签名:\_

| 论文评阅人1: | 匿名评阅人         |

|---------|---------------|

| 评阅人 2:  | ————<br>匿名评阅人 |

| 评阅人 3:  |               |

| 评阅人 4:  |               |

| T M 1 5 |               |

| 答辩委员会主席:      | 赵民建   |

|---------------|-------|

| 委员1:          | 郑史烈   |

| 委员 2:         | 余官定   |

| 委员 3:         | 林宏焘   |

| 委员 4:         | 何先华   |

| <b>委员 5</b> . | 14701 |

答辩日期: \_\_2022年3月10日\_\_\_

# 独创性声明

本人声明所呈交的学位论文是本人在导师指导下进行的研究工作及取得的研究成果。据我所知,除了文中特别加以标注和致谢的地方外,论文中不包含其他人已经发表或撰写过的研究成果,也不包含为获得\_**浙江大学**\_或其他教育机构的学位或证书而使用过的材料。与我一同工作的同志对本研究所做的任何贡献均已在论文中作了明确的说明并表示谢意。

学位论文作者签名: 发生 初宇 签字日期: 2017年 3月 12日

# 学位论文版权使用授权书

本学位论文作者完全了解 **浙江大学** 有关保留、使用学位论文的规定,有权保留并向国家有关部门或机构送交论文的复印件和磁盘,允许论文被查阅和借阅。本人授权 **浙江大学** 可以将学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存、汇编学位论文。

(保密的学位论文在解密后适用本授权书)

学位论文作者签名: 解 科宁

导师签名: 分析的

签字日期: 2022 年 3月 12日

签字日期: 7072年 3月177日

学位论文作者毕业后去向:

工作单位:

电话:

通讯地址:

邮编:

# 致谢

在浙江大学的两年半时间里,时光飞逝,岁月如梭。在研究生的学习阶段,至今依稀记得从一开始接触科研时的无知,到快毕业时,对科研有着更多的了解和认识。回忆起来,自己的每一个时光片段仍历历在目,恍若隔日。

首先,我要特别感谢我的指导老师储涛教授,在储老师的帮助下,我在研究生方向上能够不断探索,不断前行。是储老师一次次的教诲,让我能够坚持走到现在。储老师给了我很多的启发并教给我对待科研严谨的态度。老师的一言一行,都潜移默化地影响着我,让我感受到一位科研人的追求。感谢老师在我的论文上给出的意见和耐心指导,也感谢老师在我遇到问题时耐心的解答和分析。

感谢华为技术有限公司的米光灿博士,作为我的专业实践校外导师,帮助我 快速适应实习环境,带着我完整的完成了实习工作任务。后续在我撰写英文期刊 过程中,耐心帮我修改语法和文章中的问题。感谢华为公司的刘晨师姐,在我专 业实践期间也给予了我很多无私的帮助。

感谢已经毕业的林天华师兄,在我刚进入实验室阶段,带我入门,带我熟悉做实验流程,给了我数不清的指导。在我需要帮助的时候,无论是在实验室期间还是在工作之余,都会有你耐心的解答。感谢之江实验室的张磊博士,在器件制作方面,给了我很多的助力,让我能够完成相应设计器件的制作工作。同时,也离不开上海高研院的老师和同学在器件制作上的工作。感谢之江实验室的其他同事在器件测试上为我提供的帮助。

最后,我由衷感谢科研道路上每位给我帮助的老师和同学,我取得的成果离不开你们的支持和鼓励,是大家共同营造的良好科研氛围和积极的讨论促进了我的成长。感谢韩霖和李昊同学,与我一起合作完成工艺参数的确定工作。路漫漫其修远兮,吾将上下而求索。愿我在后续的时光中,永远少年,保持初心,拥抱每一个明天。

I

# 摘要

信息化时代的快速发展,推动数据通信流量快速增长,新一代的通信需求显著增加。相较于传统电互连,硅基光子集成技术能够利用光信号的带宽大和传播延迟小的特性,有效满足通信需求,且能够与 CMOS 工艺兼容,实现小体积,低功耗的光芯片设计。而光芯片与光纤之间,由于存在较大的模场尺寸之差,实现二者之间的低损耗耦合是硅光研究中的重点。光栅耦合器则是解决这一耦合问题的主流设计器件之一。本论文以单偏振低损耗设计为目标,设计了工作在不同波段的光栅耦合器。本文主要取得以下成果:

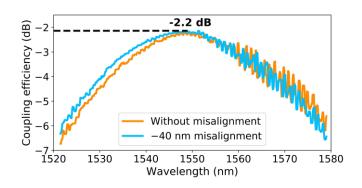

- 1. 提出一种用于多参数优化的定向优化方法,在切趾优化中实现快速收敛。 采用鲁棒性版图设计,提高器件刻蚀对准容差,结合交错刻蚀和切趾设计,实验证明光栅的耦合效率为-2.2dB。该结果为130nm CMOS工艺节点下商用硅光工艺制造的C波段硅光栅最低损耗结果。

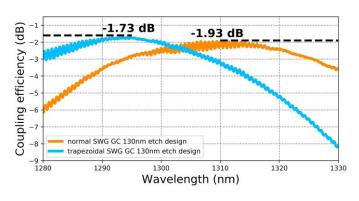

- 2. 提出一种折射率渐变的亚波长结构概念,在新型的梯形亚波长光栅结构下,实验证明单刻蚀梯形亚波长辅助光栅耦合器的耦合效率为-1.73dB,这一结果为 O 波段同类单刻蚀光栅世界最低损耗结果。

- 3. 设计并实验证明了工作在 O 波段的硅-氮化硅双层光栅耦合器,将氮化硅层设计为增透膜结构,实现高耦合效率双层切趾光栅设计,实验得到双层光栅的耦合效率为-3.15dB。

关键词:光互连,光栅耦合器,亚波长光栅,低损耗,多层光栅耦合器

浙江大学硕士学位论文 Abstract

#### **Abstract**

The rapid development of the information era has promoted the fast increasing of data flow in communication. The demand for next-generation communications has increased significantly. Compared with traditional electronic interconnection, silicon photonics integration technology exploits the wide bandwidth and low propagation loss characteristic of optical signal which makes silicon photonics has unique advantage in communication requirements. It is also compatible with CMOS process and can achieve compact and low power consumption optical chip design. However, achieving low loss coupling between optical chips and fibers is a main issue in silicon photonics researches due to large mode field mismatch. Grating coupler is one of the mainstream devices solving fiber-to-chip coupling. This paper is mainly concentrated on grating couplers designs aiming at single polarization and low loss targets. These grating couplers are contributed in different wavelength ranges respectively. This paper gets some following results:

- A directional optimized method is proposed for multi-parameters optimization. It

can achieve fast convergence during apodization process. Robust layout strategy is

used for fabrication of grating coupler which increases the tolerance of

misalignment between etch processes. The design of grating coupler combines

interleaved etch with apodization and the measured coupling efficiency is -2.2dB.

This is the lowest loss result of the C-band silicon grating couplers fabricated by

commercial silicon photonics process in 130nm-CMOS process.

- 2. The gradient change of refractive index concept is proposed. A novel trapezoidal sub-wavelength grating structure is put forward. The trapezoidal sub-wavelength single etch grating coupler achieves a measured coupling efficiency of -1.73dB. This result is the world's lowest demonstration in O band same type single etch grating couplers.

- 3. Silicon and silicon nitride dual-layer grating coupler is designed and experimentally demonstrated in O band. The silicon nitride layer is used for anti-reflector structure and contributes together with silicon layer to construct high efficiency dual-layer

apodized grating coupler design. The measurement coupling efficiency result of dual-layer grating coupler is -3.15 dB.

**Keywords:** Optical interconnection, Grating coupler, Sub-wavelength grating, Low loss, Multi-layer grating coupler.

# 目录

| 致  | 谢      |                     | I   |

|----|--------|---------------------|-----|

| 摘  | 要      |                     | II  |

| Ab | stract |                     | III |

| 目  | 录      |                     | V   |

| 1  | 绪论     |                     | 1   |

|    | 1.1    | 课题研究背景与意义           | 1   |

|    | 1.2    | 国内外研究现状             | 2   |

|    | 1.3    | 本文主要研究内容            | 9   |

| 2  | 光栅耦    | <b>禺合器工作原理及优化方法</b> | 12  |

|    | 2.1    | 光栅耦合器原理             | 12  |

|    | 2.2    | 亚波长光栅原理             | 14  |

|    | 2.3    | 光栅耦合器优化方法           | 15  |

|    | 2.4    | 本章小结                | 18  |

| 3  | C波段    | 光栅耦合器               | 19  |

|    | 3.1    | 交错刻蚀型硅光栅耦合器         | 19  |

|    | 3.1    | .1 均匀交错刻蚀光栅耦合器设计    | 19  |

|    | 3.1    | .2 基于定向优化方法的切趾光栅设计  | 21  |

|    | 3.1    | .3 高鲁棒性版图设计         | 23  |

|    | 3.1    | .4 测试结果             | 26  |

|    | 3.2    | 铌酸锂光栅耦合器            | 30  |

|    | 3.2    | 1 铌酸锂光栅耦合器设计        | 30  |

|   | 3.2.2        | 测试结果               | 34 |

|---|--------------|--------------------|----|

|   | 3.3 本        | C章小结               | 37 |

| 4 | O波段码         | E光栅耦合器             | 38 |

|   | 4.1 <i>茨</i> | 《刻蚀光栅耦合器           | 38 |

|   | 4.1.1        | 双刻蚀光栅耦合器设计         | 38 |

|   | 4.1.2        | 双刻蚀亚波长光栅耦合器设计      | 41 |

|   | 4.1.3        | 测试结果               | 43 |

|   | 4.2 单        | 2刻蚀亚波长光栅耦合器        | 44 |

|   | 4.2.1        | 单刻蚀亚波长光栅耦合器设计      | 45 |

|   | 4.2.2        | 有效媒质理论的修正          | 47 |

|   | 4.2.3        | 单刻蚀梯形亚波长光栅耦合器设计    | 49 |

|   | 4.2.4        | 测试结果               | 51 |

|   | 4.3          | 【向渐变亚波长光栅耦合器       | 54 |

|   | 4.3.1        | 双向渐变亚波长光栅耦合器设计     | 54 |

|   | 4.3.2        | 测试结果               | 56 |

|   | 4.4 本        | <b>、</b> 章小结       | 57 |

| 5 | 硅-氮化矿        | 佳多层光栅耦合器           | 59 |

|   | 5.1 -        | 一种高效宽带光栅耦合器设计      | 59 |

|   | 5.2 码        | 上氦化硅光栅耦合器          | 61 |

|   | 5.2.1        | 氮化硅参数的确定           | 61 |

|   | 5.2.2        | 硅光栅-氮化硅增透膜结构设计     | 62 |

|   | 5.2.3        | 硅光栅-氮化硅增透膜结构设计测试结果 | 63 |

|   | 5.2.4 | 硅-氮化硅双层切趾光栅设计   | 66 |

|---|-------|-----------------|----|

|   | 5.2.5 | 硅-氮化硅双层切趾光栅测试结果 | 70 |

|   | 5.3 硅 | 三氮化硅优化参数光栅耦合器   | 76 |

|   | 5.3.1 | 氮化硅优化参数的确定      | 76 |

|   | 5.3.2 | 硅-氮化硅双层光栅耦合器设计  | 77 |

|   | 5.3.3 | 硅-氮化硅多层光栅耦合器设计  | 79 |

|   | 5.4 本 | 章小结             | 81 |

| 6 | 总结与展  | 望               | 83 |

| 参 | 考文献   |                 | 87 |

| 作 | 者简历   |                 | 92 |

### 1 绪论

### 1.1 课题研究背景与意义

随着集成电路行业的快速发展,集成电路中器件的特征尺寸逐渐缩小到 10nm 量级,当该尺寸逐渐接近原子尺寸时,摩尔定律的进一步发展开始面临一系列问题[1]。电学互连在高密度芯片间通信,高性能计算以及数据中心等领域应用时,无法满足高数据容量和高速的通信需求<sup>[2]</sup>。光学互连相较于电学互连具有带宽大,损耗低,传播延迟小等特点,因此成为解决通信需求增长的可行互连方案 [3]。此外,由于互补金属氧化物半导体(CMOS)工艺在集成电路产业中的不断完善,与传统 CMOS 工艺兼容的硅光子技术能够依托于成熟工艺条件实现制造 [4]。同时,硅光芯片设计能够实现小尺寸,低功耗的光芯片设计。这些优点使得硅光子技术极具研究价值。

绝缘体上硅结构(SOI)晶圆被广泛应用于硅光子技术领域<sup>[5]</sup>。低损耗波导 <sup>[6]</sup>,光开关<sup>[7]</sup>和调制器<sup>[8]</sup>等器件,都成功在 SOI 晶圆上实现了实验验证。在硅光子技术中,由于光芯片上波导尺寸与光纤间存在较大的物理尺寸上的差异,直接使用光纤与光芯片进行耦合,会带来较大的损耗问题<sup>[9]</sup>。目前主要有两种结构设计的器件被用于解决这一损耗问题:分别是光栅耦合器和端面耦合器。端面耦合器在光芯片上利用模斑扩束结构,于芯片边缘或者切片得到的端面位置实现与光纤间的低损耗输入/输出<sup>[10]-[12]</sup>。相较于端面耦合器,光栅耦合器通过光栅结构实现垂直芯片表面的衍射,因此可以在光芯片任意位置进行排布。尤其是在大规模集成应用中,能够实现更高密度的光学耦合<sup>[13]</sup>。与此同时,光栅耦合器无需切片得到端面,能够支持晶圆级测试。

光栅耦合器的研究主要集中于低损耗光栅,偏振分集光栅<sup>[14]</sup>和宽带光栅<sup>[15]</sup>设计三个方面。对于光栅的低损耗研究,是大部分光栅设计的目标之一。无论是偏振分集光栅应用还是宽带光栅应用,也都需要降低相应器件的损耗,抑或是在损耗和其他性能之间进行权衡。因此,低损耗光栅设计在光栅耦合器的研究中成为主流的研究设计方向。

1

### 1.2 国内外研究现状

在 SOI 晶圆上,通过刻蚀工艺在顶层硅上形成一系列刻蚀和未刻蚀区域交替的周期性结构,能够实现光栅器件的制作。单偏振光栅耦合器的损耗主要受到三个因素的影响:因光栅结构在芯片法线方向上的结构对称性,带来向衬底方向传播的泄露损耗;在与单模光纤耦合过程中,因光栅输出场分布与单模光纤高斯场分布不同,带来的模场失配损耗;以及向输入光方向的背反射损耗。在光栅耦合器的设计中,通常会在光纤与光栅表面的芯片法线方向之间引入一个小角度倾角,通过这种方法能够有效抑制背反射损耗。所以小角度耦合的光栅耦合器设计过程中,低损耗设计主要围绕降低模场失配损耗和泄露损耗展开。而降低光栅耦合器的损耗,由于光栅耦合器在传输过程中的应用,也对应于对光栅耦合效率的提升。

2004年,Taillaert等人设计了首个在 SOI 晶圆上的光栅耦合器。通过在 220nm 顶层硅的 SOI 晶圆结构上,利用数值仿真优化,得到埋氧层(BOX)厚度和上包层厚度的最优值 $^{[16]}$ 。最终分别在均匀光栅结构和非均匀光栅结构下,得到仿真设计结果。这里的非均匀光栅是通过改变光栅不同周期内的光栅参数实现相应的结构设计,非均匀设计能够改变光栅的输出场分布形式,有效解决因为与单模光纤之间模场失配问题带来的损耗。而这种非均匀设计方法也被称为切趾(apodized)设计。在后续工作中,由于切趾设计无需引入额外的工艺,所以被研究者们进行了广泛的探索与应用。在与单模光纤耦合的应用场景中,需要考虑与单模光纤模场尺寸的匹配问题。2006年,Taillaert等人在制作光栅耦合器过程中,将垂直于波导中光传播方向的光栅耦合区域尺寸宽度设计为  $12\mu m$ ,用于与  $10.4\mu m$  的光纤模场直径相匹配 $^{[17]}$ 。为实现单模波导与  $12\mu m$  宽波导区域的过渡,设计中使用  $400\mu m$  长的线性扩束结构,完成在波导宽度方向的低损耗模场转换。这种结构就成为光栅耦合器基本的结构设计。

而对于光栅耦合器垂直方向对称性带来的衬底泄露损耗,主要可以通过在光栅耦合器所在顶层硅的下方制造金属反射镜<sup>[18]</sup>或者底部 DBR 反射镜<sup>[19]</sup>的结构来降低相应的损耗。这两种结构可以有效反射原本向衬底泄露的光能量,实现对泄露损耗的补偿作用。有的研究还利用镜面反射的原理,通过聚焦离子束工艺制作出具有一定倾角的闪耀光栅结构,在光能量经过光栅区域实现一定角度的镜面反

射,有效降低衬底泄露损耗[20]。尽管这些结构设计能够有效解决光能量向衬底方向传播的泄露损耗问题,但是由于相应结构无法在标准商用硅光 CMOS 兼容工艺中进行制造,使得这些结构难以实现大规模生产应用。因此,近年来的低损耗光栅耦合器的研究主要集中在 CMOS 兼容工艺条件下的高耦合效率光栅设计。与此同时,随着硅光技术的发展,硅基光波导的研究日趋成熟,为实现硅光波导在平板中的单模传输条件,SOI 晶圆的顶层硅厚度在大部分硅光商用代工厂中开始使用 220nm 顶层硅的晶圆结构[21]。所以 220nm 顶层硅 SOI 晶圆结构的光栅设计,成为低损耗光栅研究的核心设计目标。与此同时,也有一些研究在不考虑工艺实现条件下,着眼于新型光栅结构设计,追求获得更高耦合效率的突破性结果。

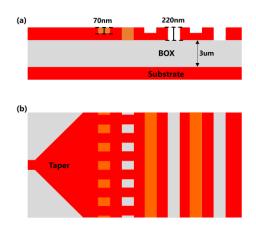

国外研究进展: 由于实际工艺制作过程中的最小线宽限制,模场失配损耗无法通过简单的单刻蚀结构切趾设计实现完美的损耗补偿。此外,光栅耦合器的泄露损耗也很难在商用硅光工艺有限几个刻蚀深度的单刻蚀结构下降低。为提高光栅耦合器的耦合效率,2015年,日利纳大学的DANIEL BENEDIKOVIC等人首次使用由70nm和220nm交替刻蚀形成的交错刻蚀结构<sup>[22]</sup>,如图1.1 所示。这种设计能够有效结合两种常用的商用硅光工艺刻蚀深度,打破垂直方向上的对称性,一定程度上形成类似于闪耀光栅的结构,实现对耦合效率的提升。此外,在光栅耦合器前端靠近扩束结构区域的刻蚀槽内,引入垂直光传播方向的亚波长光栅结构。通过这种亚波长光栅设计,有效降低光栅前端的泄露损耗和模场失配损耗。最终在220nm 顶层硅晶圆以及100nm 最小线宽制作条件下,实现C波段下峰值测试耦合效率为-1.3dB的结果。

图 1.1 交错刻蚀结合亚波长光栅设计示意图[22]

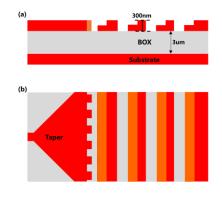

在交错型刻蚀的基础上, 虽然能够有效提高光栅耦合器的整体性能, 但是在 两次不同刻蚀深度刻蚀槽间的光栅齿结构,会影响类似闪耀光栅结构的衍射,不 能充分模拟闪耀光栅反射镜的作用。因此,2017年巴黎萨克雷大学设计了 L 型 结合 SWG 设计的光栅耦合器[23],设计结构如图 1.2 所示。L 型结构是通过两次 不同深度刻蚀的一定距离位移,形成 L 型的类阶梯结构。通过 L 型结构,更为 直接的模拟了闪耀光栅的设计,进一步降低光栅泄露损耗。最终在 300nm 顶层 硅,100nm 最小线宽的电子束光刻(EBL)条件下,在C波段测试得到的峰值耦 合效率为-2.7dB。该设计的主要问题在于 L 型结构对于两次刻蚀对准有极高的要 求,尽管设计上有相对交错刻蚀结构更优的结果,但是在实际制作过程中,得到 的测试结果反而低于2015年的交错刻蚀亚波长光栅设计。在这一设计的基础上, DANIEL BENEDIKOVIC 等人继续增加亚波长光栅结构所在光栅周期的数量,通 过对亚波长结构的进一步设计,实现 C 波段仿真耦合效率为-0.25dB 的结果[24]。 但很显然的是, 无论是 L 型结构的高刻蚀对准容差问题, 还是更多的亚波长光栅 结构,都增加了工艺的复杂度,这些问题也导致该设计未进行后续的实验制造。 为解决 L 型结构在制造上的问题, 有的研究考虑通过设计进一步放宽最小线宽 限制,增强相应结构的工艺可实现性。2020年,加拿大国家研究委员会将亚波长 结构全部设计在 L 型结构远离波导的全刻蚀槽内的位置,通过亚波长结构填充 相应区域,降低由全刻蚀引起的背反射损耗[25]。同时,由于亚波长结构相当于减 小光栅前端区域的有效折射率对比度,原本对光栅前端小尺寸刻蚀槽的需求被一 定程度上放宽。最终在 106nm 最小线宽下,实现了在 C 波段-1.46dB 的仿真耦合 效率。该结果同样未得到相应的测试结果,这些相关研究均揭示了 L 型结构光栅 在提高光栅耦合效率上的作用,同时也反映出 L 型结构在工艺制造上的难度。

图 1.2 L 型结合 SWG 光栅设计示意图[23]

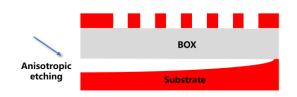

在基础的扩束结构结合光栅的设计上,为了进一步减小由于从单模波导到光 栅区域宽波导的模场转换扩束结构的尺寸, Van Laere F 等人考虑将光栅区域与 扩束区域一起进行横向波导的扩束,原本的条形光栅也转变为圆弧形光栅结构, 用于实现小尺寸聚焦型光栅设计[26]。通过这种设计形式,能够有效减小光栅耦合 器的设计尺寸,提高光栅耦合器的集成度。目前主流的光栅研究在130nm CMOS 工艺节点下进行,其耦合效率会受到最小线宽的限制。尽管大多研究中已经采用 相应节点下 100nm 的极限线宽值进行设计和电子束光刻制造,但是耦合效率仍 旧未能进一步提高。2018年 Luxtera 在光纤通信会议(OFC)上,通过演讲的形 式介绍了在台湾积体电路制造公司(TSMC)的65nm节点工艺下,实现的多次 刻蚀结构高耦合效率聚焦型光栅设计[27]。该设计通过使用领先的工艺节点,实现 了耦合效率的大幅度提升。与此同时,聚焦型光栅设计通过将光栅耦合区域和扩 束结构一起设计为扇形形式,能够降低光栅耦合器的整体尺寸。在制作光栅过程 中,将光栅顶层硅上方的所有介质层通过刻蚀工艺全部去除,有效避免了二氧化 硅上包层以及上层其他材料介质层的影响,进一步提升整体器件性能。最终测试 得到的峰值耦合效率在 C 波段中高于-1dB。当然这种领先工艺节点的设计,与目 前文章中主流的光栅设计不具备很明显的对比效果,且上包层整体刻蚀结构,极 容易对光栅器件带来测试过程中的环境污染,对器件的稳定性产生影响。此外, 由于金属反射镜结构能够有效降低光栅损耗,也有研究立足于设计可用于 CMOS 兼容工艺下的底部金属反射镜型光栅耦合器。2019年,贝尔实验室将光栅耦合 器设计在芯片端面位置,通过各向异性刻蚀去掉端面光栅底部的埋氧层,如图 1.4 所示[28]。在此基础上于底部镀金形成金属反射镜,有效反射泄露光能量,实现光 栅在 C 波段下,峰值耦合效率-1.3dB 的测试结果。该结构的优点在于无需使用 键合工艺,就能够在 SOI 晶圆上制造得到底部金属反射镜辅助的光栅。但是,这 种设计却限制了光栅原本可以自由排布的优势。同时其相应的制造工艺较为复杂, 在应用到商用硅光工艺中需要一定的工艺制造上的优化以及额外工艺的引入。

图 1.4 端面各向异性刻蚀光栅设计示意图[28]

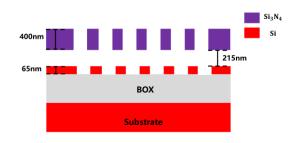

为解决光栅耦合器的损耗问题,除了在硅光栅上的一系列结构设计外,也有研究通过引入 CMOS 兼容工艺中的其他介质层,在垂直方向上提高光能量的方向性,降低光栅泄露损耗。在 CMOS 兼容工艺中,最常见的介质层是硅层上方的氮化硅材料,因此,这种多层介质的光栅设计主要以氮化硅-硅作为相应的设计结构。2014 年多伦多大学采用 150nm 顶层硅结构的 SOI 晶圆,在氮化硅-硅工艺平台上,实现高耦合效率宽带光栅设计的制作<sup>[29]</sup>,其器件结构如图 1.3 所示。通过垂直方向上的氮化硅层和硅层共同作用,形成在垂直方向上更高模场的复合模式,而较高的模场能够抑制泄露损耗的产生,最终提高光栅的整体耦合效率。在 C 波段下实现了峰值耦合效率-1.29dB 以及 1dB 带宽 80nm 的测试结果。尽管该结构需要相对较薄的顶层硅以及距离顶层硅 50nm 间距的氮化硅层实现设计,但是这种光栅作为可以直接在商用硅光工艺中制造的设计,仍旧具有较高的研究价值。

图 1.3 氮化硅-硅双层光栅设计示意图[29]

光栅耦合器的研究主要集中在 C 波段应用的设计上。另外,由于光栅耦合器结构与波长相关性强,这导致 C 波段光栅耦合器的高效设计无法直接在 O 波段进行复制,需要探索属于 O 波段的低损耗设计方案。于国外研究中,为降低 O 波段光栅耦合器的损耗,同样考虑采用多刻蚀结构实现不同刻蚀深度的结合,实现在工艺制作中的最小线宽限制下的标准 220nm SOI 晶圆结构上的设计。2014年 Institute of Microelectronics 的 Ruizhi Shi 等人首次采用 60nm 和 130nm 两种刻

蚀深度,在 220nm 顶层硅的 SOI上,在靠近扩束结构(taper)前端光栅区域采 用 60nm 作为刻蚀深度,后端光栅区域的刻蚀深度为 130nm 的光栅耦合器[30]。 最终在 1302nm 中心波长下,得到光栅的测试耦合效率为-2.0dB。但是,两种刻 他深度的刻蚀工艺,很容易会在制作过程中,受到不同刻蚀工艺间的对准误差问 题,带来相应的制作偏差。同时,两次刻蚀实现整体光栅的制造流程也增加了工 艺制作难度。因此,2016年巴黎萨克雷大学在220nm深度的单次刻蚀条件下, 通过借鉴 C 波段中的亚波长光栅结构,实现了在 O 波段测试耦合效率为-2.5dB 的实验结果[31]。该设计仅需一次刻蚀,即可完成整体的制造流程,充分简化了光 栅器件的工艺制作流程,同时也获得了一定耦合效率的测试结果。由于引入氮化 硅层,能够有效提升光栅器件的性能。因此,在双层光栅设计的基础上,2018年 多伦多大学在硅-氮化硅-氮化硅平台上,继续进行多层光栅的设计工作,具体设 计将下层氮化硅作为光传输层,通过上层氮化硅层,顶层硅层以及光传输层的光 栅结构,实现三层光栅的最终设计[32]。最终在 O 波段实现了测试耦合效率为-3.5dB 的实验结果。该实验结果相对其他研究来说损耗较高,这主要是由于在多 层光栅设计下, 受限于同时制作的其他器件结构对氮化硅结构参数的需求(层间 耦合结构和交叉波导结构), 使得氮化硅层在当前结构下没有起到对结果的优化 作用, 甚至在一定程度上影响了整体性能。因此多层光栅在 O 波段的设计有待 于进一步研究探索。

国内研究进展:与国外2014年多伦多大学硅-氮化硅高耦合效率设计相类似,同样使用硅-氮化硅多层光栅结构对耦合效率进行提升,2015年华中科技大学的ZouJ等人进一步将硅-氮化硅高耦合效率结构应用到220nm顶层硅SOI晶圆上,通过优化氮化硅层到硅层的间距,以及氮化硅和硅层的光栅结构参数,将硅层设计为氮化硅层的反射层,提高光栅耦合器的整体耦合效率[33]。最终实现了仿真耦合效率-0.88dB的设计结果。该结果由于在硅层和氮化硅层同时使用了100nm的最小线宽,具有较高的工艺制造难度,未得到相应的器件制造结果。

在这些设计结构基础上,为了进一步提升光栅的方向性,降低泄露损耗。2020年,北京大学一个课题组发表在一篇发表在自然期刊上的论文中,基于拓扑光子学的理论分析,精确控制刻蚀的侧壁倾角,实现了超高方向性的光栅耦合器设计 [34],其结构如图 1.5 所示。该结构能够在一对拓扑分量的光相互耦合作用下,实

现对光能量几乎单一方向的衍射,最终实验测得了超过 1.6×10<sup>5</sup> 的方向性结果。 这一实验结果基本实现了对泄露损耗问题的完美解决,但是如何将高精度倾斜刻 蚀应用到商用硅光工艺中,仍旧需要进行很多实验和工艺上的探索。

图 1.5 基于拓扑光子学的倾斜刻蚀光栅示意图[34]

完美垂直耦合光栅耦合器,也即是不引入光芯片与光纤之间小角度倾角的光栅耦合器设计。相较于传统光栅设计,完美垂直耦合光栅需要同时考虑对背反射损耗的降低,对低损耗设计提出了更高的要求。对于 O 波段低损耗光栅的研究,2017年浙江大学一个课题组,通过化学方法对晶圆的埋氧层进行腐蚀,实验制造得到了一种倾斜膜结构的光栅耦合器<sup>[35]</sup>,如图 1.6 所示。该光栅结构不使用传统设计中小角度倾角的耦合,利用光栅区域的倾斜结构,有效消除背反射影响,实现低损耗完美垂直耦合光栅设计。实验测得光栅耦合效率为 O 波段下-2.44dB。

在表 1-1 中,将国内外的低损耗光栅耦合器研究进行汇总说明。其中制作工艺主要通过电子束光刻 (EBL)和 CMOS 工艺对光栅设计进行区分。制作工艺中的 Si 表示 SOI 晶圆顶层硅厚度,CD 指的是光栅设计的最小线宽尺寸。/表示相应文章中未给出制作工艺或在测试损耗中未进行相应结构的制造和测试工作。

图 1.6 倾斜膜结构光栅示意图[35]

表 1-1 低损耗光栅耦合器国内外研究现状

| 年份   | 波段  | 设计结构             | 制作工艺                         | 测试损耗    | 参考文献 |

|------|-----|------------------|------------------------------|---------|------|

| 2014 | C波段 | 硅-氮化硅<br>双层光栅    | CMOS<br>150nm Si<br>200nm CD | -1.3dB  | [29] |

| 2015 | C波段 | 交错刻蚀<br>SWG 结构   | EBL<br>220nm Si<br>100nm CD  | -1.3dB  | [22] |

| 2017 | C波段 | L 型结构<br>SWG 结构  | EBL<br>300nm Si<br>100nm CD  | -2.7dB  | [23] |

| 2018 | C波段 | 多刻蚀<br>聚焦光栅      | CMOS<br>65nm CD              | -1.0dB  | [27] |

| 2019 | C波段 | 各向异性刻蚀 底部金属      | /                            | -1.3dB  | [28] |

| 2019 | C波段 | L型结构<br>SWG 结构   | 220nm Si<br>100nm CD         | /       | [24] |

| 2020 | C波段 | L 型结构<br>SWG 结构  | 220nm Si<br>106nm CD         | /       | [25] |

| 2014 | O波段 | 双刻蚀硅光栅           | CMOS<br>220nm Si<br>200nm CD | -2.0dB  | [30] |

| 2016 | O波段 | 单刻蚀硅光栅<br>SWG 结构 | EBL<br>220nm Si<br>100nm CD  | -2.5dB  | [31] |

| 2017 | O波段 | 倾斜膜结构<br>垂直耦合光栅  | EBL                          | -2.44dB | [35] |

| 2018 | O波段 | 硅-氮化硅<br>三层光栅    | CMOS<br>65nm Si<br>200nm CD  | -3.5dB  | [32] |

# 1.3 本文主要研究内容

本文参照光栅耦合器的主流低损耗设计方案,结合光栅相关原理,在C波段和 O 波段分别开展单偏振低损耗光栅耦合器设计。在无底部金属反射镜和底部分布式反射镜结构的前提下,设计并测试得到了商用硅光工艺制作的 140nm 最小线宽最低损耗 C 波段硅光栅耦合器;在 O 波段上,测试得到了已知文章中最

低损耗的单刻蚀光栅耦合器。

本文共分为六章,第一章对低损耗光栅耦合器的可行设计思路及一些 CMOS 兼容工艺下的光栅设计结构和新型光栅设计结构进行了介绍;第二章从光栅耦合器的原理出发,对光栅的后续章节设计和优化方法做理论层面的分析;第三章主要是围绕工作在 C 波段下的交错刻蚀硅光栅设计和铌酸锂光栅设计展开;第四章展示了工作在 O 波段的硅光栅耦合器设计,包括双刻蚀光栅,双刻蚀亚波长光栅以及不同亚波长光栅结构的单刻蚀光栅耦合器;第五章介绍了工作在 O 波段的硅-氮化硅多层光栅结构的单刻蚀光栅耦合器;第五章介绍了工作在 O 波段的硅-氮化硅多层光栅耦合器,在两种氮化硅结构参数下,分别进行了硅-氮化硅双层光栅的设计,在优化后的氮化硅参数条件下进行硅-氮化硅-氮化硅三层光栅设计;第六章对整体研究生期间的工作进行了总结,并对遇到的一些问题进行思考与展望。

#### 本文的创新点:

- 1. 提出一种定向优化方法,基于不同结构参数的权重定义最优仿真方向,提高光栅仿真的收敛速度。能够支持光栅耦合器多参数优化仿真。提出一种高鲁棒性设计的版图方法,通过扩展多次刻蚀中后续刻蚀工艺的掩膜,在商用硅光工艺中,增加光栅设计在多次刻蚀之间的对准容差。设计并实验证明了交错刻蚀与切趾结合的 C 波段光栅耦合器,成功测试得到在 140nm 最小线宽约束下,无 SWG 和其他材料层的商用硅光工艺最低损耗硅光栅。在 1549nm 中心波长下,测试耦合效率为-2.2dB。

- 2. 设计了一种单刻蚀梯形结构亚波长光栅耦合器,在 130nm 单刻蚀条件,EBL 工艺条件下,实现在 O 波段的世界最低损耗单刻蚀硅光栅结果。在 1295nm 中心波长下,得到的测试耦合效率为-1.73dB。首次提出两种新型的亚波长光栅结构,在 70nm 均匀结构的前提下,六边形 SWG 光栅和圆角矩形 SWG 光栅,在新加坡 AMF 流片得到测试耦合效率分别为-2.95dB 和-3.3dB。相较于相同工艺常规均匀光栅的-4.15dB 实验结果提升接近 1dB 的耦合效率。

- 3. 提出了不同结构的 O 波段多层光栅耦合器,通过硅-氮化硅多层设计,将氮化硅层设计为增透膜结构,利用高耦合效率的硅层光栅结构,共同作用提高光栅的整体耦合效率,首次在新加坡 AMF 代工厂进行实验验

证。得到硅-氮化硅双层切趾光栅的最优测试耦合效率为-3.15dB。

# 2 光栅耦合器工作原理及优化方法

本章通过对光栅耦合器原理的分析,充分阐释光栅耦合器设计的理论依据。 从理论层面揭示了不同设计方法的出发点。此外,本章还介绍了对光栅耦合器的 仿真软件和优化设计方法,提出了一种支持多参数切趾优化的定向优化方法。

### 2.1 光栅耦合器原理

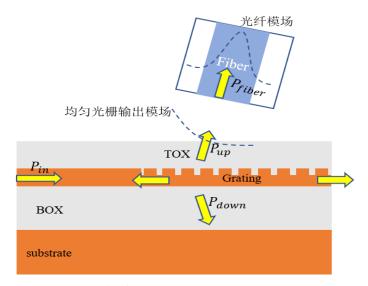

以输出光栅为例,光在光栅中的光路径如图 2.1 所示进行传播。当光从波导中传输到光栅位置时,由于光栅结构带来的有效折射率周期性变化,使得光不再严格限制在波导中,形成向上衍射和向下衍射的光能量。另外,也会存在一部分未能在光栅长度范围内衍射的光能量以及向光输入方向传播的背向反射能量。

图 2.1 光栅耦合器光路图(以输出光栅为例)

光栅耦合器的工作原理可以从干涉原理出发进行分析。根据射线光学理论, 当光经过光栅结构时,在不同光栅周期的界面处发生衍射,多个界面的光共同作 用,最终在光栅的输出端满足建设性干涉条件<sup>[36]</sup>。光栅原理如公式(2-1)所示。

$$p = \frac{m\lambda_0}{n_{eff} - n_0 \sin \theta} \tag{2-1}$$

其中,p表示光栅的周期,m为光栅的衍射级次, $\lambda_0$ 是光栅传输曲线中耦合效率最高处的波长,也就是光栅器件的中心波长, $n_0$ 指的是光栅上包层介质的有效折射率, $\theta$ 为光纤与光芯片法线方向的夹角, $n_{eff}$ 是光栅整体结构的有效折射率。(2-1)公式也被称为光栅的基本方程,建立了光栅不同结构参数之间的关系。

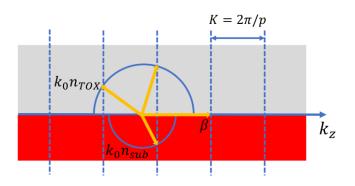

在光栅的设计过程中,首先需要对光栅的衍射级次进行确定。其中,光栅的衍射级次与耦合输入/输出的角度直接相关。二者之间的关系,可以通过 k 空间中的分析得出[37]:

$$k_{m} = \beta + mK \tag{2-2}$$

其中, $k_m$ 表示沿光波导中光的传播方向,m 衍射级次的波矢量。 $\beta$  为光栅中光学模式的有效传播常数,K 与光栅周期 p 成反比。此时,向上和向下衍射以及背向反射的光能量就可以由各自所在介质的折射率和光栅结构参数共同决定,如图 2.2 所示。其中, $n_{TOX}$  表示上包层材料的有效折射率, $n_{Sub}$  表示组成光栅结构的材料有效折射率。从提高器件集成度的角度考虑,零级衍射级能够尽可能避免输入/输出倾角  $\theta$  的产生,也即是在 k 空间中满足  $K=\beta$  的关系,具有实现更高集成度的潜力。但是在这一衍射级次条件下,会产生在波导中除输入/输出光能量外的衍射光分量,如公式(2-3)所示。

图 2.2 光栅耦合器 k 空间波矢示意图

这时,(2-3)公式的光分量与光在波导中的传播方向相反,会引入向输入光方向很强的背向反射,这种背向反射光能量会在测试曲线中产生谐振现象以及增加器件的耦合损耗。所以在光栅耦合器的设计中,较多地采用-1级衍射级进行设计。在-1级衍射级下,既可以有相对高衍射级次较小的出射角度,增加光栅耦合器的集成度;同时也能够有效抑制背反射损耗。在实际设计过程中,通过引入一个与芯片表面垂直方向 10°左右的小角度光纤倾角,在 k 空间中可以实现光栅在-1 衍射级下的输入/输出。

为研究光能量经过光栅的耦合效率,需要探究光栅内的能量分布情况。根据一阶扰动分析方法,Tamir 和 Peng 探究多种光栅分布形式,最终确定了光栅能量与传播距离的关系<sup>[38]</sup>:

$$P = P_0 \exp(-2\alpha z) \tag{2-4}$$

其中  $P_0$  表示输入进光栅的光能量, $\alpha$  表示第 m 衍射级的泄露因子(也被称为光栅强度或扰动强度),其大小决定了光栅衍射光强度的能力。z 表示从 taper 区域指向光栅耦合区域方向的位置坐标,坐标原点为光栅 taper 与光栅耦合区域的分界面。由(2-4)的公式就能得出能量随位置坐标 z 变化的关系:

$$\frac{dP(z)}{dz} = -2\alpha P(z) \tag{2-5}$$

同时,因为光是一种电磁波,在电磁场中,同样满足能量与电场(磁场)的平方成正比的关系,所以有:

$$\frac{dP(z)}{dz} = -B^2(z) \tag{2-6}$$

公式 (2-6) 中的负号表示沿z 方向传播时,光能量在经过光栅衍射过程中逐渐衰减。B(z)表示在z 位置处的电场强度。在光栅耦合器常用的切趾设计中,设计改变的就是泄露因子的数值,也即是在整个光栅区域形成特定的泄露因子分布。所以  $\alpha$  也是与位置有关的参量,在后续公式中改写为 $\alpha(z)$ 。结合公式 (2-5) 和 (2-6),可以建立电场分布与泄露因子之间的关系:

$$\alpha(z) = \frac{B^{2}(z)}{2[P_{0} - \int_{z_{0}}^{z} B^{2}(t)dt]}$$

(2-7)

这里的 $P_0$ 表示在输出光栅光传播方向上,光栅耦合区域与taper结构的分界线坐标 $z_0$ 位置处的光能量。该公式为后续章节的光栅切趾设计以及提出的优化方法提供了理论依据。

# 2.2 亚波长光栅原理

在对光栅器件进行理论分析时,光栅的周期性结构使得其有效折射率不能像常规体材料一样直接分析得到。光栅的周期长度一般为亚微米量级,这种小尺寸且不连续的整体光栅结构,可以通过有效媒质理论(EMT)分析,进而得到光栅的有效折射率<sup>[39]</sup>。此外,有效媒质理论还会受到偏振态的影响,结合光的电场偏

振方向与波导中光传播方向的关系,在不同的偏振态下得到相应的有效折射率计算公式。EMT 在不同偏振态下的关系如公式(2-8)和(2-9)所示:

$$n_{eff}^2 = (1 - f) \cdot n_0^2 + f \cdot n_{gc}^2$$

(2-8)

$$\frac{1}{n_{eff}^2} = \frac{1 - f}{n_0^2} + \frac{f}{n_{gc}^2} \tag{2-9}$$

(2-8)对应横向电模式(TE)的光栅有效折射率计算公式,(2-9)对应横向磁模式(TM)的计算公式。f表示光栅的占空比参数,具体到光栅中是指在一个光栅周期内,未刻蚀区域长度占整个光栅周期长度的比例。ngc 为光栅所使用材料的模式有效折射率。在实际设计过程中,(2-8)和(2-9)的公式仅适用于全刻蚀光栅的情况。在分析浅刻蚀光栅的有效折射率时,原本(1-f)刻蚀区域中的 no不再对应包层的有效折射率,而是由部分垂直光传播方向上的光栅所使用材料构成的等效介质。所以需要在设计浅刻蚀光栅中,对刻蚀区域 no 进行同样方法的EMT 计算,得到相应刻蚀深度下刻蚀区域垂直方向的全结构有效折射率,进而得到最终的整体光栅有效折射率。

根据光栅的 EMT 分析,可以通过调整光栅的占空比,一定程度上实现对整体结构有效折射率的调整。在光栅耦合器的设计中,常采用亚波长光栅(SWG)结构填充常规光栅的刻蚀槽区域,有效降低相应刻蚀区域与光栅齿间的有效折射率差<sup>[22]</sup>。后续的亚波长光栅设计以及对亚波长光栅方程的优化以本节的有效媒质理论作为基础进行相应的工作。

# 2.3 光栅耦合器优化方法

光学结构的仿真,需要对其结构和结构所在区域的电磁场进行求解,得到最终光学结构的设计结果。本文使用基于有限时域差分方法(finite difference time-domain method)的商用 Lumerical 软件,完成光栅耦合器的仿真设计工作。该软件结合 FDTD 方法的思想,实现对仿真结构的求解。FDTD 方法利用中心差商代替场量对时间和空间的偏导数,能够有效求解三维 Maxwell 方程。通过将三维空间网格化,在时间上模拟计算,综合设置的边界条件,对几个波长范围内的结构能够得到较为准确的仿真计算结果[40]。

在光栅耦合器的设计过程中,对光栅的多个结构参数进行优化,能够得到最终的优化结果。在多个参数优化过程中,需要相应的优化方法来完成。同时,由于常见的光栅耦合器具有多个光栅周期,当进行切趾优化设计时,每个光栅周期内的占空比和周期长度都需要进行优化处理,这种优化上的需求增加了光栅器件仿真的复杂度和仿真时间。因此,选择合适的优化算法,在光栅设计中也十分重要。

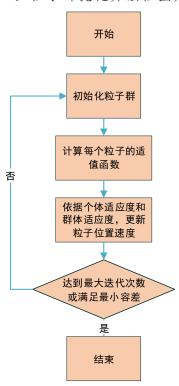

光栅设计最常用的优化方法为粒子群优化 (PSO) 方法, 粒子群优化方法的来源是模拟鸟类的捕食行为,对每个优化得到的解都设置相应的适值函数来判断当前值的优劣,使解空间的各个解都具有记忆以及自主追求最优解的惯性。另外,每个粒子同时具有一个面向最优解方向的速度。在多轮迭代的过程中,解粒子可以通过适值函数,优化搜索过程中的记忆以及群体最优经验来调整仿真的速度和方向,从而不断靠近最优解<sup>[41]</sup>。粒子群优化算法框图如图 2.3 所示。

图 2.3 粒子群优化算法框图

当优化的参数数量进一步增加时,常用的粒子群优化方法需要相应增加仿真的代数和每代仿真的粒子数。此外,粒子群优化方法在优化参数过多时,需要对很多个适值函数进行不断的优化,在多个适值函数的多个最优解的排列组合之中,得到最优的排列组合,这一过程造成仿真难度大幅度增加,甚至出现无法在有限

代数条件下搜索到最优值的情况。为解决这一问题,有的研究采用了线性切趾的方法以实现光栅耦合器的切趾优化<sup>[42]</sup>。在线性切趾方法下,将光栅从 taper 区域指向光栅耦合区域的占空比设置为线性变化,如公式 (2-10) 所示:

$$f(i) = f_0 - R \cdot z(i) \tag{2-10}$$

$f_0$ 表示切趾变化的初始占空比值,R是线性切趾变化参数,其大小表示线性切趾过程中占空比线性变化的速度。z(i)为光栅第i个周期的z方向位置坐标,f(i)代表第i个光栅周期的占空比。在线性切趾方法中,能够在较少的优化参数条件下,改变光栅不同周期内的占空比,减小光栅结构靠近 taper 区域的光能量泄露损耗。同时,这种占空比的变化能够降低光栅输出场分布与光纤输出场分布间的失配损耗。

在对光栅多个结构参数进行优化设计的过程中,基于多因子权重优化思路,本文提出了一种定向优化方法。在进行光栅耦合器的设计时,由于硅光工艺中对图形的最小线宽会有要求,所以需要在设计时进行相应的结构最小尺寸限制<sup>[43]</sup>。同时,在 2.1 节中经过理论分析,均匀光栅的光场分布服从 e 指数衰减形式,这种分布导致光能量在光栅耦合区域靠近 taper 部分衍射出的光能量相较其他区域更多<sup>[38]</sup>。综合考虑光栅场分布和最小线宽问题的限制,本节提出了一种多权重因子定向优化方法。在多参数的切趾设计中,给每个光栅周期定义一个权重参数,具体权重的定义如公式(2-11)所示<sup>[44]</sup>。

$$\begin{cases} W_{i1} = \frac{P_g(i) / P_f(i)}{\sum_{1}^{n_{-}periods} [P_g(i) / P_f(i)]} & i = 1, 2 \cdots n_{-}periods \\ W_{i2} = \frac{P_g(i)}{\sum_{1}^{n_{-}periods} P_g(i)} & i = 1, 2 \cdots n_{-}periods \\ W_i = W_{i1} \cdot W_{i2} \end{cases}$$

(2-11)

$P_g$ 是指光栅中的光能量,光能量在均匀光栅的整个光栅结构区间内满足 e 指数衰减分布,其具体的能量分布函数由光栅结构参数决定。 $P_f$ 则是光纤中的光能量,标准单模光纤的光场能量呈高斯分布。在整体光栅有  $n_i$  periods 个周期时,第 i 个光栅周期的权重表示为  $W_i$ ,而每个光栅周期的权重由两个归一化权重参量组成。 $W_{i1}$  表示考虑最小线宽限制的归一化权重参量,当该权重越大时,表示越容易受到最小线宽的制约,也更容易找到最优值。因此在相应的周期下, $W_{i1}$

权重大的光栅周期具有更高优先级的搜索排序。 $W_{i2}$  表示模拟光能量分布影响的归一化权重参数,该权重表示在能量较大的光栅区域内的结构参数,具有对光栅仿真结果更强的影响,在优化上具有更高的优先级 $^{[45]}$ 。

在将不同光栅周期进行权重赋值后,将权重按照由高到低的顺序排序。依据排序结果,进行相应顺序的优化。该优化方法能够快速找到仿真最优值,提高光栅器件的优化收敛速度。定向优化方法将应用于后续章节的具体设计之中,通过第三章与 PSO 方法的对比,进一步说明该仿真方法的优势。同时,该方法能够结合 PSO 优化方法一起使用,在不考虑仿真设计时间和计算成本时,可以通过定向优化方法给出的方向,在一定数量光栅周期的组合下使用 PSO 进行进一步优化。定向优化方法也能够有效解决 PSO 在多参数条件下无法在有限代数内搜索到最优值的问题。

### 2.4 本章小结

本章基于光栅耦合器的工作原理,介绍了光栅器件结构参数间的关系以及后续章节切趾设计的理论依据。阐述了亚波长光栅原理,为后续亚波长光栅相关结构设计及对有效媒质理论的修正工作奠定基础。此外,本章还对光栅耦合器的仿真软件及光栅耦合器的优化方法进行了介绍,在2.3节中提出了一种用于多参数优化的定向优化方法,提高了光栅耦合器的仿真效率以及在多参数优化场景下搜索最优解的能力。

# 3 C波段光栅耦合器

本章介绍了 C 波段光栅耦合器的相关设计,分别在 SOI 晶圆以及铌酸锂晶圆上,完成对光栅耦合器的仿真和测试工作。对于 SOI 晶圆上的硅光栅耦合器,通过结合交错刻蚀结构和切趾方法,实现高耦合效率的器件设计。应用第二章中的定向优化方法,在均匀交错刻蚀结构上,完成切趾型交错刻蚀光栅设计。同时,在相同的均匀交错刻蚀结构下进行 PSO 和定向优化方法的仿真,对比 PSO 优化方法得到定向优化方法的优势。在版图设计中,通过扩展后续刻蚀工艺对应的光刻胶掩膜,实现商用硅光工艺中高刻蚀对准容差的光栅耦合器制作结果。此外,本章还介绍了 C 波段铌酸锂光栅的设计,结合灰度刻蚀和切趾结构,在实验室工艺中实现与其他铌酸锂器件兼容的设计和制作结果。

### 3.1 交错刻蚀型硅光栅耦合器

在 C 波段硅光栅耦合器的设计中,通过交错刻蚀及亚波长光栅结构设计,能够实现极低损耗的器件性能制作结果<sup>[22]</sup>。但是这种光栅设计在刻蚀过程中受到亚波长光栅小尺寸结构滞后效应的影响,会带来光栅器件损耗性能的不可控恶化<sup>[46]</sup>。因此,具体到本节的 C 波段硅光栅设计,以商用硅光工艺场景的高鲁棒性和高耦合效率的光栅设计为目标,借鉴采用交错刻蚀的结构,与切趾方法结合实现光栅耦合器的最终设计。

# 3.1.1 均匀交错刻蚀光栅耦合器设计

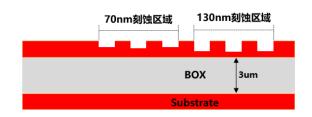

在商用硅光工艺中,220nm 顶层硅 SOI 晶圆常用的顶层硅刻蚀深度为 70nm, 130nm 和 220nm<sup>[47]</sup>。由于考虑借鉴使用交错刻蚀设计结构,需要用到两种不同深度的刻蚀工艺。而不同刻蚀深度的组合,在交错刻蚀结构中会有不同的耦合效率性能。具体设计需要考虑到实际耦合角度与交错刻蚀形成的类 L 型结构的关系。出射角度在第二章的分析中,可以得出是一个接近 10°的参量。而无论是 70nm 和 130nm 还是 130nm 和 220nm 的刻蚀深度组合,都会形成一个角度较小的反射镜结构,这种结构无法在较小光纤角度条件下实现整体光能量的高耦合效率输出

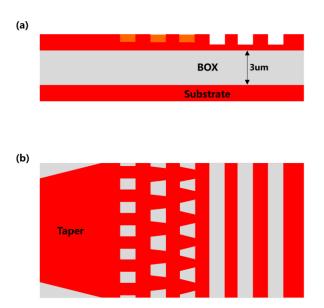

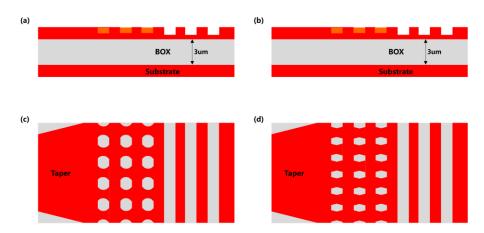

/输入。因此,本节设计的交错刻蚀结构采用商用硅光工艺的 70nm 和 220nm 两种深度的刻蚀工艺,实现对整体光栅设计结构的定义,具体结构如图 3.1 所示。

图 3.1 交错刻蚀型光栅结构示意图。(a) 交错刻蚀光栅剖面图。(b) 交错刻蚀 光栅俯视图。(c) 交错刻蚀光栅剖面光场分布图。

在图 3.1 中, $g_1$  和  $g_2$  分别表示 70nm 刻蚀深度的刻蚀槽和 220nm 全刻蚀的刻蚀槽宽度, $I_1$  和  $I_2$ 则是将  $g_1$  和  $g_2$  分开的光栅齿区域宽度。在这一设计基础上,考虑商用硅光工艺的最小线宽问题。在 130nm CMOS 硅光工艺节点下,由于光栅具有密集线条结构,硅光代工厂对于光栅器件的最小线宽会有相对其他器件更严格的要求 $[^{48]}$ 。传统器件在 130nm CMOS 硅光工艺节点下,能够实现 100nm 的最小器件尺寸的结构制作。而光栅器件则只能在 140-150nm 最小线宽下,保证稳定的制作结果。因此,本节设置 140nm 作为交错刻蚀型硅光栅的最小设计线宽。在所有的光栅周期内,保证刻蚀槽宽度和光栅齿宽度均 $\geq 140$ nm。通过 Lumerical的 2D-FDTD 软件进行仿真,以 C 波段 TE 模式单偏振光栅的耦合效率作为优化目标,仿真优化  $g_1$ 、  $g_2$ 、  $I_1$ 、  $I_2$  和光纤倾角  $\theta$  五个结构参数。其中,综合考虑集成度和背反射问题,将光纤倾角  $\theta$  仿真优化范围设置为 8-15° 。利用 <math>PSO 优化方法,对均匀交错刻蚀型光栅进行仿真设计。在光纤倾角为 15°, $g_1$ 、  $g_2$ 、  $I_1$ 和  $I_2$ 分别取值  $I_3$ 2 分别取值  $I_4$ 3 以及  $I_5$ 3 以  $I_5$ 4 以  $I_5$ 4 以  $I_5$ 5 以  $I_5$ 4 以  $I_5$ 5 以  $I_5$ 6 以  $I_5$ 6 以  $I_5$ 7 以  $I_5$ 8 以  $I_5$ 8 以  $I_5$ 9 以  $I_$

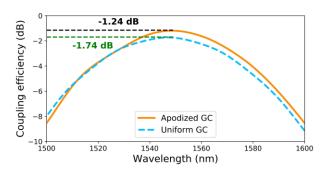

图 3.2 交错刻蚀光栅传输曲线

### 3.1.2 基于定向优化方法的切趾光栅设计

尽管通过结构上的优化和设计,均匀型光栅设计能够得到较高耦合效率的设计结果。但是均匀光栅在输出光能量场分布中,总会满足 e 指数衰减形式。在与光纤进行耦合的过程中,与光纤的高斯模场不匹配会带来一定的模场失配损耗。通过切趾的设计方法,将均匀光栅设计为不均匀的形式,能够有效降低模场失配损耗。因此,本节在 3.1.1 节中的均匀交错刻蚀光栅设计的基础上,继续进行切趾优化,进一步提升光栅的耦合效率。使用第二章中提出的定向优化方法,对光栅设计进行仿真。将不同光栅周期的权重进行赋值排序。在均匀光栅中,光栅的能量分布满足 e 指数衰减形式。因此,代表能量的权重从 taper 指向光栅耦合区域也同样符合 e 指数衰减的函数关系。对于代表线宽的权重,根据函数关系可以通过 e 指数衰减函数与光纤中光模场的高斯函数之比,获得线宽制约因素下,不同光栅周期的优化优先级权重。得到不同光栅周期的权重如表 3.1 所示。

| 7=       |         |         |         |         |         |         |         |         |

|----------|---------|---------|---------|---------|---------|---------|---------|---------|

| 周期数      | 1       | 2       | 3       | 4       | 5       | 6       | 7       | 8       |

| 总权重      | 0.2325  | 6.4e-06 | 4.8e-10 | 9.8e-14 | 5.4e-17 | 8.1e-20 | 3.3e-22 | 3.7e-24 |

| 线宽权 重    | 0.9998  | 0.0002  | 1.1e-07 | 1.7e-10 | 6.9e-13 | 7.7e-15 | 2.3e-16 | 1.9e-17 |

| 能量权<br>重 | 0.2325  | 0.0314  | 0.0042  | 0.0006  | 7.8e-05 | 1.1e-05 | 1.4e-06 | 1.9e-07 |

| 周期数      | 9       | 10      | 11      | 12      | 13      | 14      | 15      |         |

| 总权重      | 1.1e-25 | 9.1e-27 | 2.0e-27 | 1.2e-27 | 2.0e-27 | 9.1e-27 | 1.1e-25 |         |

| 线宽权 重    | 4.2e-18 | 2.6e-18 | 4.2e-18 | 1.9e-17 | 2.3e-16 | 7.7e-15 | 6.9e-13 |         |

| 能量权<br>重 | 2.6e-08 | 3.5e-09 | 4.8e-10 | 6.5e-11 | 8.8e-12 | 1.2e-12 | 1.6e-13 |         |

表 3.1 不同光栅周期权重计算结果

根据表 3.1 得到的权重关系,按照总权重由高到低的顺序对不同光栅周期进 行排序。对光栅结构参数按照相应的排序进行迭代扫描优化。其中, 在权重排序 过的方向下, 具体优化过程是通过对相应顺序下的光栅结构参数使用 Lumerical FDTD 中的 sweep 功能进行相同顺序的仿真,不断优化光栅的耦合效率。为保证 仿真结果的准确性,对扫描的整体过程进行多次迭代,得到最终的仿真优化结果。 这里的多次迭代扫描,是在所有结构在给定优化方向完成一轮优化后,再次进行 计算得到下一轮的权重,根据新一轮权重排序结果,进行迭代优化。提出的定向 优化方法在优化过程中,不同于粒子群优化方法的地方在于:定向优化根据物理 原理的分析,给出指定的优化方向,极大地提高了仿真效率,不再需要大量的数 学层面的训练或仿真代数积累,即可找到其他算法需要迭代获得的优化方向。而 PSO 优化方法从数学原理上对参数进行一定程度的扫描和训练,在仿真结果的 积累下,寻找到最优方向。但是这种方式不可避免地面临优化参数增加时难以找 到最优值的问题,需要大量的仿真得到最终结果,对多参数优化问题存在一定缺 陷。最终在定向优化方法下,得到切趾仿真的结果如图3.2中的橘黄色实线所示。 在 1550nm 中心波长下, 交错刻蚀结合切趾设计光栅的峰值耦合效率为-1.24dB。 由此可见,交错刻蚀结合切趾的结构相较于均匀交错刻蚀光栅具有 0.5dB 的耦合 效率提升。

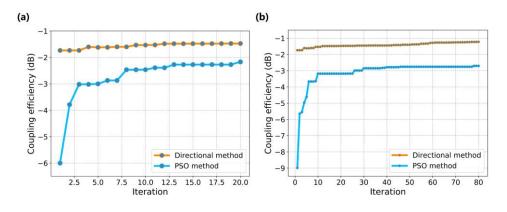

为证明定向优化方法的优势,在本章 3.1.1 节仿真得到的均匀交错刻蚀光栅结构基础上,分别采用定向优化方法和粒子群优化方法对均匀型交错刻蚀光栅进行后续的切趾仿真验证。在两种优化方法下的仿真优化过程如图 3.3 所示。

图 3.3 定向优化方法与粒子群优化方法仿真优化过程示意图。(a) 20 个优化参数条件的两种方法优化过程。(b) 40 个优化参数条件的两种方法优化过程。

在图 3.3 (a) 中, 首先选取前五个光栅周期内的结构参数进行仿真对比。在 两种深度的刻蚀作用下,共有二十个优化参数(每个光栅周期内有  $g_1$ 、  $g_2$ 、  $I_1$ 和 6 四个参数)进行仿真优化。在进行仿真对比的过程中,两种方法的每次迭代 扫描点数均设为30个。通过图中的结果可以看出,定向优化方法能够有效利用 均匀光栅仿真的结果,在 20 次迭代中,将耦合效率从均匀光栅的-1.74dB 提升到 -1.48dB。而粒子群优化方法,则需要对 20 个参数同时进行搜索,这一优化参数 数量超出相应仿真设置下的粒子群优化方法的优化能力,在 20 次仿真迭代后仍 旧处于-2.15dB 这一没有优于均匀光栅的仿真结果。其实,在这种前 5 周期的仿 真中, 粒子群优化已经一定程度上借鉴了定向优化方法的优势, 在前 5 个周期 内,正好是定向优化方法权重最高的区域。此时, PSO 方法仍旧没有获得优于定 向优化方法的仿真结果。 所以, 为进一步排除粒子群优化中定向优化的作用, 继 续将仿真参数数量增加, 削弱定向优化方法在粒子群优化方法中的作用。同时, 在更多优化参数的仿真中, 也更能体现出定向优化方法在多参数优化过程中的优 点。后续在图 3.3 (b) 中, 选取前十个光栅周期内的四十个参数进行两种方法的 仿真对比。在每次迭代扫描点数为30个,仿真迭代80代后,定向优化方法几乎 达到最终的切趾优化结果,此时仿真耦合效率为-1.25dB。在一定的仿真容差内, 60 代优化后的定向优化仿真过程可以认为达到收敛条件。粒子群优化方法则由 于优化的参数继续增加,更加难以搜索到最优值,在80代后的仿真耦合效率结 果仅为-2.7dB。因此, 第二章中提出的定向优化方法能够有效借助均匀光栅的仿 真结果,在均匀光栅设计基础上完成后续的切趾优化设计。而且在多参数优化场 景下,该方法能够快速找到切趾的优化参数,有效提高仿真效率。

# 3.1.3 高鲁棒性版图设计

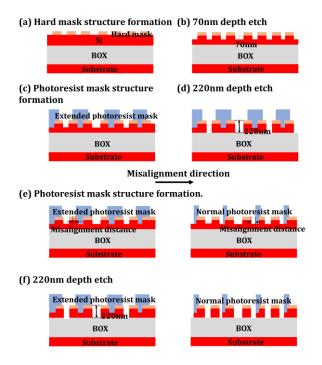

在交错刻蚀结构下,由于结构具有 70nm 和 220nm 两种刻蚀深度,在制造过程中需要两次刻蚀及刻蚀对应的两次光刻工艺来实现相应的光栅结构。然而,不同刻蚀工艺之间,会因为不同光刻流程的对准误差问题,带来一定的制造误差,影响器件的最终性能。因此,本节提出了一种高鲁棒性版图设计,通过版图上的优化,提升光栅对不同深度刻蚀间的对准容差。高鲁棒性版图在具体的制造工艺中,其制造过程如图 3.4 所示。

在图 3.4 (a-d) 中,70nm 刻蚀以商用硅光工艺中的硬掩膜结构作为保护层,形成的掩膜一直存在于顶层硅的所有刻蚀工艺中,起到对不需要刻蚀的顶层硅区域的保护作用<sup>[49]</sup>。在硬掩膜结构保护下,实现对无硬掩膜区域70nm 深度的刻蚀。随后,当工艺进行到220nm 深度的刻蚀时,利用提出的高鲁棒性版图方法,能够充分考虑沿光传播方向刻蚀对准误差的影响,将光刻胶掩膜在光传播方向上进行扩展,形成220nm 刻蚀工艺对应的光刻胶结构。具体到设计中,扩展的光刻胶掩膜宽度为70nm 刻蚀区域两侧光栅齿宽度的一半,这样就会将不同刻蚀的对准容差提升到最小光栅齿宽度的1/2,这一对准容差在3.1.2节中的设计为70nm。在图 3.4 (e-f) 里,对不同刻蚀间发生对准误差的情况进行分析,在扩展型光刻胶掩膜结构下,尽管220nm 刻蚀对应的光刻胶发生整体偏移,但由于扩展型光刻胶在对准误差方向上的补偿作用,仍然能够得到仿真预期的制造结果。而常规结构的光刻胶则会出现偏离光栅设计的制造结果。

图 3.4 高鲁棒性版图设计与常规版图设计对比的交错刻蚀型光栅制造流程。

(a) 硬掩膜结构制造流程。(b) 70nm 深度刻蚀工艺。(c) 扩展光刻胶掩膜制造流程。(d) 220nm 深度刻蚀工艺。(e) 对准误差条件下扩展型版图设计 vs 常规版图设计光刻胶掩膜制造流程。(f) 两种版图设计对应的制造结果

为了更好地说明这一版图设计的作用,在仿真结构中引入±70nm 的刻蚀对准误差进行仿真模拟,在 2D-FDTD 中对扩展型版图设计和常规版图设计在刻蚀对准误差条件下进行了仿真对比。仿真结果如图 3.5 所示。

设置负方向为从光栅耦合区域指向 taper 的方向,在图 3.5 (a)中,可以看到在+70 nm 或-70 nm 刻蚀对准误差下,扩展型版图设计能够与无刻蚀对准误差时的设计保持相同的传输曲线不变。而常规版图设计的光栅在+70 nm 刻蚀对准误差条件下,中心波长偏移到 1519 nm。在-70 nm 刻蚀对准误差条件下,仿真光栅的中心波长小于 1500 nm。另外,在 1550 nm 波长下,两种刻蚀对准误差条件对常规版图设计的光栅带来的最高附加损耗大于 20 dB。在图 3.5 (b)中,展示了 ±70 nm 刻蚀对准误差变化对常规版图设计影响的仿真结果。为更清晰地说明对准误差方向性的影响,在图 3.5 (b)中的插图给出了负方向对准误差对常规

图 3.5 (a) ±70 nm 刻蚀间对准误差条件下,扩展型版图设计和常规版图设计仿真传输曲线。(b) -70~+70nm 刻蚀对准误差对常规版图设计影响仿真结果,插入的图例给出对刻蚀对准误差负方向的定义以及负方向刻蚀对准误差在常规版图设计中形成的制造结果。

版图方法制造光栅结构的示意图。通过仿真得到的曲线可以看出,负方向刻蚀对准误差相比正方向对器件性能影响更大。这是因为在负方向的刻蚀对准误差下,制造的光栅结构形成垂直于光耦合输出/输入方向的类反射镜结构,这种结构比正方向刻蚀对准误差条件下的结构对耦合效率的影响更为明显。

# 3.1.4 测试结果

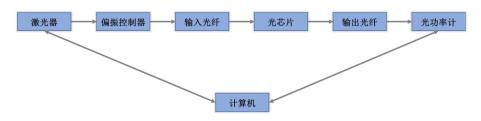

光栅耦合器的测试系统主要由图 3.6 中的测试系统框图组成。由激光器输入相应波长的光能量,经过偏振控制器调节输入光的偏振态,由于本文设计的光栅耦合器以 TE 模式单偏振低损耗作为设计目标,所以此过程通过偏振控制器将偏振态调整为 TE 模式。光能量经过输入光纤垂直耦合输入到光芯片中。从光芯片的输出,经由输出光纤输出到光功率计上得到相应的接收光功率。在垂直耦合台中调整好耦合状态后,通过计算机控制激光器和光功率计,实现一定波长范围内的扫描,得到最终的光栅测试传输曲线的原始数据。

图 3.6 光栅耦合器测试系统框图

在图 3.7 中,展示了测试系统中用到的垂直耦合测试台,光功率计以及激光器。图 (a) 为垂直耦合测试台,被用于实现光芯片与输入/输出光纤的三维对准,找到相应器件的最佳耦合位置。图 (b) 为测试使用的 SANTEC 激光器,用于产生对应波段的输入光源。图 (c) 为测试输出光能量大小的 EXFO 光功率计。

图 3.7 光栅测试系统照片。(a) 垂直耦合测试系统照片 (b) 激光器照片 (c) 光功率计照片

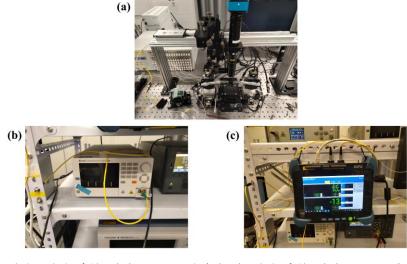

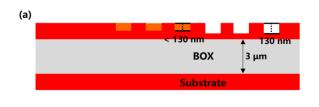

在商用硅光代工厂 Compound Tek 的 SOI 晶圆上,完成对 C 波段硅光栅设计的制造。其中使用的 SOI 晶圆具有 220nm 顶层硅厚度和 3μm 厚度的埋氧层。在不同次刻蚀工艺流程中,采用 193nm 深紫外光刻工艺形成对应结构的掩膜图形定义,光栅器件的最小制作线宽为 140nm。器件的制造结果如图 3.8 所示。

图 3.8 交错刻蚀光栅扫描电子束显微镜(SEM)结果图 (a) 光栅耦合区域平面 SEM 图 (b) 光栅耦合区域的细节 SEM 图表 3.2 均匀和切趾型交错刻蚀光栅测试结果

| 类别                               | 刻蚀宽度变化 | 损耗<br>(dB/coupler) |

|----------------------------------|--------|--------------------|

| -<br>IG1 刻蚀区域宽度 -<br>比例补偿 -      | 80%    | /                  |

|                                  | 90%    | ~10                |

|                                  | 100%   | 2.8                |

|                                  | 110%   | 3.6                |

|                                  | 120%   | 7                  |

| -<br>IG1 刻蚀区域宽度 -<br>定值补偿 -<br>- | -40nm  | 20                 |

|                                  | -30nm  | 15                 |

|                                  | -20nm  | 9                  |

|                                  | -10nm  | 5                  |

|                                  | +10nm  | 2.6                |

|                                  | +20nm  | 5                  |

|                                  | +30nm  | 7                  |

| -<br>IG2 刻蚀区域宽度 -<br>比例补偿 -      | 80%    | /                  |

|                                  | 90%    | 20                 |

|                                  | 100%   | 3.65               |

|                                  | 110%   | 3.45               |

|                                  | 120%   | 8.5                |

| IG2 刻蚀区域宽度<br>定值补偿               | -10nm  | 5                  |

|                                  | +10nm  | 3.4                |

|                                  | +20nm  | 5                  |

|                                  | +30nm  | 7                  |

在制造过程中设计光栅耦合区域的宽度为 12μm,为避免光栅宽度方向的对准误差影响,制造光栅的 70nm 刻蚀区域设计为 14μm。而这一补偿设计,使得光栅耦合器在宽度方向两侧,产生了 70nm 深度的扩展刻蚀槽结构。在测试过程中,首先在光纤角度固定的条件下,对不同结构光栅进行测试,测试得到均匀交错刻蚀光栅和切趾交错刻蚀光栅在不同的线宽补偿组下,实验结果如表 3.2 所示。

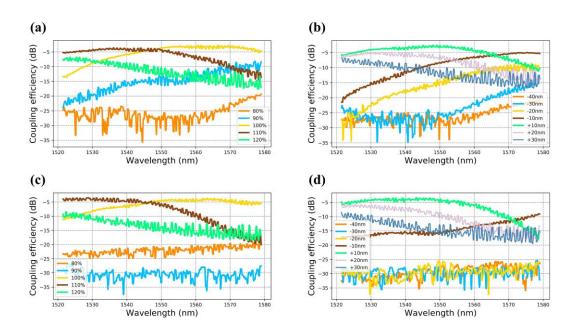

测试过程均采用 12 度光纤倾角进行测试,通过测试结果初步筛选较优损耗的器件设计。在表 3.2 中,IG1 为切趾型交错刻蚀光栅设计,IG2 表示均匀型交错刻蚀光栅设计。为保证最终实验得到的器件能够获得仿真设计的结果,分别设计了刻蚀槽宽度定值补偿组和比例补偿组进行实验。通过补偿组实验设计,能够在工艺发生偏差时,仍旧得到符合仿真的器件制造结果。表中/在损耗一栏中表示损耗超过 20dB,对最终设计结果参考价值不高。根据测试结果可以看出,两组测试结果均在+10nm 线宽补偿组中,取得相应设计的最优测试值。同时,IG1和 IG2 测试结果对比,发现 IG1 比 IG2 测试耦合效率高 0.8dB,这一结果能够有效证明切趾型交错刻蚀结构相较于均匀型交错刻蚀结构对耦合效率有明显的提高作用。得到的相应测试传输曲线如图 3.9 所示。

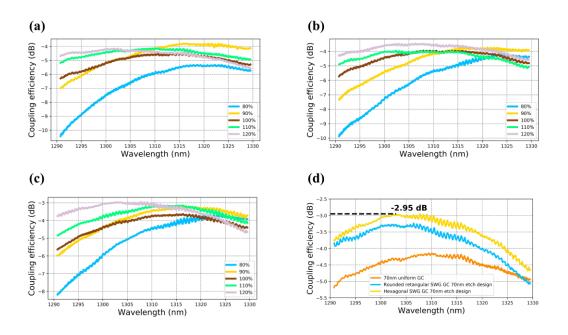

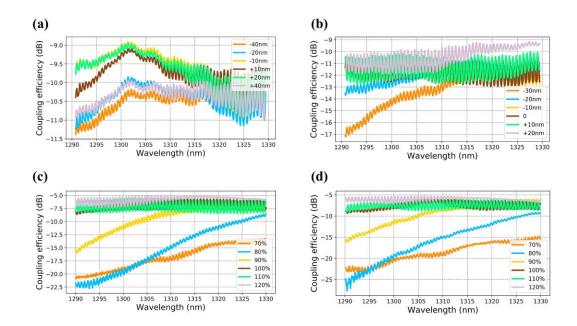

图 3.9 交错刻蚀光栅测试结果。(a) 交错刻蚀切趾光栅比例补偿实验组。(b) 交错刻蚀切趾光栅定值补偿实验组。(c) 均匀交错刻蚀光栅比例补偿实验组。(d) 均匀交错刻蚀光栅定值补偿实验组。

在图 3.9 中的结果可以看出,图 (a) 中的交错刻蚀切趾光栅线宽不进行补偿的测试组,在相同的光纤倾角下,中心波长偏离了 1550nm。因此,对测试过程中该组光栅进行仔细对准以及调整光纤角度,通过将光纤角度调整为 14°,利用光纤角度变化将中心波长移动到仿真预期值,从而得到与仿真设计对应的器件制造测试结果。在之前的实验过程中,由于耦合对准实验次数较多,总会造成一定的三维耦合平台的偏移以及未寻找到最佳耦合位置的问题。与此同时,为了验证提出的版图设计的鲁棒性,在实验过程中,于对照组的版图额外引入-40nm 的刻蚀对准误差,在同样的设计结构下完成整体制造流程。引入负方向的刻蚀对准误差进行对比试验,是根据仿真中负方向的刻蚀对准误差相对正方向影响较大,进行的相应版图设置。基于这些实验上的改进,在后续实验测试中测得的结果如图 3.10 所示。

图 3.10 无刻蚀对准误差及-40nm 刻蚀对准误差下的交错刻蚀型切趾 光栅测试结果。

图 3.10 中,蓝色曲线为引入-40nm 刻蚀对准误差时,交错刻蚀切趾光栅测试结果。橘黄色曲线为实际制造工艺中,不在版图中额外引入刻蚀对准误差的交错刻蚀切趾光栅测试结果。得到光栅器件在不额外引入刻蚀对准误差时,在1549nm 中心波长下,测试峰值耦合效率为-2.2dB,3dB 带宽 47nm。而引入-40nm刻蚀对准误差时,两次测试结果在较小的误差范围内,曲线重叠较好,表明本文的版图方法能够提升器件的刻蚀对准容差,引入的-40nm刻蚀对准误差没有对光栅器件测试耦合效率产生影响。测试曲线中,在 1560-1580nm 波长范围内,光栅器件测试耦合效率产生影响。测试曲线中,在 1560-1580nm 波长范围内,光栅器件的传输曲线上具有相对其余测试波长范围较为明显的谐振。这主要是由于交错刻蚀中全刻蚀结构设计,会不可避免地带来一定的背反射损耗,而背反射是引起光栅曲线谐振的主要因素之一。而谐振现象对波长范围的选择性,是因为切趾

方法的引入在 1520-1560nm 波长范围内抑制了背反射能量, 所以导致仅在 1560-1580nm 波长范围内出现明显的谐振。-2.2dB 的测试结果为无其他介质材料和 SWG 结构的 140nm 最小线宽 C 波段商用硅光工艺制造的最低损耗硅光栅测试结果。

# 3.2 铌酸锂光栅耦合器

相对硅材料, 铌酸锂 (LN) 材料具有较高的电光系数和良好的非线性效应, 这使得铌酸锂材料在高速电光调制和非线性光学领域极具优势<sup>[50]-[51]</sup>。由于铌酸锂材料的一系列优点, 在铌酸锂材料上的相关器件研究日益增多。对于铌酸锂材料的晶圆结构, 如何实现光芯片与光纤的高效耦合, 同样是一个需要解决的问题。目前对高耦合效率的铌酸锂光栅设计也吸引了一部分的研究<sup>[52]-[54]</sup>。因此, 本节结合实验室的铌酸锂工艺条件, 开展 C 波段的 LN 光栅设计。

#### 3.2.1 铌酸锂光栅耦合器设计

铌酸锂光栅的设计采用 600nm 顶层铌酸锂厚度, 4.7μm 埋氧层 (BOX) 的 绝缘体上铌酸锂结构 (LNOI) 的晶圆结构。上包层厚度为 800nm, 铌酸锂层刻 蚀深度为 200nm。这些工艺参数主要是综合其他铌酸锂器件和波导结构得出的最优设计值。结合实验室工艺条件,以步进式光刻机的具体性能指标来设置光栅设计中的最小线宽限制。实验室工艺能够在 500nm 最小线宽条件下对结构实现稳定制作,最高可以制作 400nm 线宽的结构,但是不能保证在每次实验过程中均得到稳定的实验结果。而本节的研究则是在考虑与其他铌酸锂器件设计相兼容条件下,不引入额外的工艺,实现低损耗铌酸锂光栅的设计。因此,在相对硅光栅设计更为严格的最小线宽条件下实现一定耦合效率的铌酸锂光栅仿真,是本节的主要研究内容。

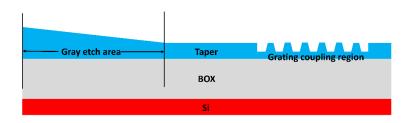

铌酸锂材料折射率比硅材料折射率低,这种较低的材料折射率与包层材料的 折射率差相对较小,导致光栅结构对光能量的束缚能力较弱,这种较低的折射率 对比度结构在光栅耦合器中引入较大的泄露损耗。同时,考虑到希望铌酸锂的刻 蚀深度和顶层铌酸锂厚度与其他铌酸锂器件设计保持一致,不引入额外的工艺增 加工艺复杂度,对于泄露损耗问题没有办法通过调整刻蚀深度的方式进行优化。 因此,将其他铌酸锂器件中的灰度刻蚀工艺引入铌酸锂光栅设计中,用于解决泄露损耗的问题,设计结构如图 3.11 所示。灰度刻蚀是通过激光直写工艺在芯片的不同区域上形成不同厚度的光刻胶掩膜。在随后的刻蚀工艺过程中,不同厚度的光刻胶会使得刻蚀在进行到不同时间时被去除,从不同的时间开始继续刻蚀形成不同刻蚀深度区域的灰度斜坡结构<sup>[55]</sup>。通过这种工艺结合常规光栅设计,能够在工艺参数固定下,不改变其他铌酸锂器件和波导结构设计,实现对光栅耦合区域晶圆厚度的优化。在刻蚀深度为 200mm 时,降低向衬底方向的泄露损耗,得到最终的铌酸锂光栅设计结果。

图 3.11 灰度刻蚀型铌酸锂光栅设计示意图

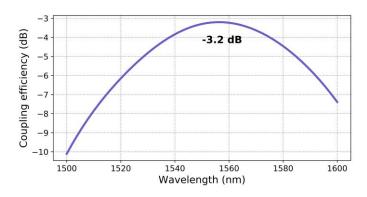

对铌酸锂光栅的设计,首先采用 500nm 最小线宽进行仿真,仿真过程中通过 Lumerical 中的代码限制每个周期的光栅齿和刻蚀槽宽度不小于最小线宽值。结合图 3.11 中的设计结构,使用粒子群方法优化光栅区域的整体铌酸锂晶圆高度,也即是通过灰度刻蚀工艺从 600nm 晶圆厚度降低到光栅区域的铌酸锂晶圆高度。在 FDTD 软件的粒子群优化中同时也对光纤耦合倾角,铌酸锂光栅的光栅长度和光栅占空比参数进行优化。优化得到在光栅区域的铌酸锂整体厚度为400nm,光纤倾角 16°,铌酸锂光栅周期 1μm 以及铌酸锂光栅占空比为 50%时,于 1550nm 波长下得到均匀光栅的耦合效率为-3.3dB。在这一均匀结构的基础上,对均匀光栅不同光栅周期的周期长度和刻蚀槽宽度进行切趾优化,通过 FDTD 软件中的 sweep 功能进行参数迭代扫描,最终优化得到的仿真光栅传输曲线如图 3.12 所示。

图 3.12 切趾铌酸锂光栅仿真传输曲线

从图 3.12 中可以看出,在 500nm 最小线宽条件下,得到中心波长 1558nm 的切趾型铌酸锂光栅仿真峰值耦合效率为-3.2dB。

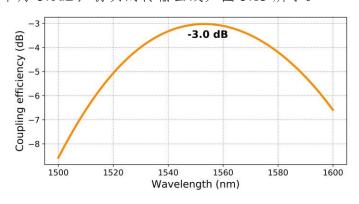

为保证仿真能够得到预期的制作结构,本节进一步考虑铌酸锂器件制作过程中的问题。在制作铌酸锂材料的光栅耦合器时,实际铌酸锂刻蚀工艺配方的一定侧壁倾角结构以及刻蚀过程带来光栅区域刻蚀槽宽度扩展的问题,都会对铌酸锂光栅最终的制造产生影响。在铌酸锂光栅仿真中,将侧壁刻蚀倾角以及线宽畸变的工艺条件加入具体设计中,使仿真设计更贴近于实验结果。在加入这两点工艺影响后,对铌酸锂光栅设计采用 400nm 最小线宽进行 2D-FDTD 仿真,利用 FDTD 软件的粒子群优化方法,优化铌酸锂光栅的光纤倾角,光栅周期,光栅占空比以及光栅耦合区域的晶圆高度。仿真得到在光纤倾角为 6°,光栅周期为 960nm,光栅占空比为 52.76%以及光栅耦合区域的铌酸锂厚度为 390nm 时,铌酸锂光栅的峰值耦合效率为-3.0dB,仿真的传输曲线如图 3.13 所示。

图 3.13 400nm 最小线宽的灰度刻蚀均匀铌酸锂光栅传输曲线

在这一均匀结构的基础上,考虑引入切趾方法对光栅设计继续进行的优化。 在具体的切趾设计中,不同于一般的光栅设计过程,在实验室铌酸锂工艺条件下, 波导缩窄问题会导致刻蚀槽宽度相较于光栅齿宽度更难制作出小线宽结构。基于 这一工艺前提进行分析,对于某一光栅周期而言,光栅在占空比较小和较大时,可以有相同的光栅强度,而光栅强度在占空比为 0.5 时,光栅强度最强。因此可以使用光栅刻蚀槽宽度较大的设计结构取代常用的刻蚀槽宽度较小的前端区域光栅设计,充分利用工艺条件中波导缩窄带来的刻蚀槽宽度增加问题。因此,铌酸锂光栅在这种工艺条件下,更适合引入第二章中介绍的线性切趾优化方法。将线性切趾参数设置为负数,此时沿着光栅方向,刻蚀槽宽度递减。这样的设计能够在光栅靠近 taper 的区域,通过较小的光栅齿宽度实现光栅前端较弱的光场输出能量。有效解决因波导缩窄工艺带来的线宽改变问题。

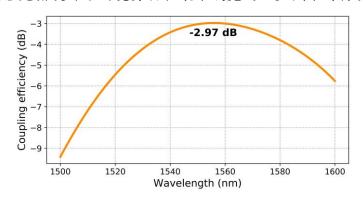

在 FDTD 中对灰度刻蚀均匀铌酸锂光栅进行线性切趾优化。优化得到的结果表明: 当线性切趾参数为-0.2, 起始占空比为 70.4%以及截止占空比为 50.2%时,取得光栅耦合效率的最优值。这里的起始占空比表示光栅靠近 taper 位置的初始光栅占空比,而截止占空比表示当光栅按照线性关系变化,不小于截止占空比值。这一截止占空比的设置是为了在光栅远离 taper 的区域,能够在获得接近0.5 的占空比值时,不再进一步按照线性关系减小光栅强度,从而降低与光纤光场分布之间的模场失配损耗。仿真得到在1556nm 中心波长下,峰值耦合效率为-2.97dB,光栅的仿真传输曲线如图 3.14 所示。从仿真结果中可以看出,由于最小线宽的限制,尽管已经考虑工艺问题进行相应的切趾优化处理,但是耦合效率还是没有明显的提升效果。而切趾方法的结果很大程度上受限于最小线宽。所以该方法在铌酸锂光栅设计中的优势会在最小线宽进一步减小时得以体现。

图 3.14 线性切趾灰度铌酸锂光栅仿真传输曲线

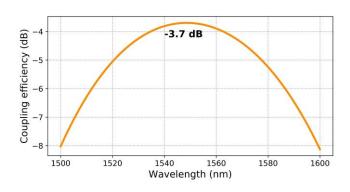

为保证实际制作过程中能够得到稳定的制作结果,采用相同的优化方法对 500nm 最小线宽的铌酸锂光栅进行仿真设计。同样基于 PSO 优化方法得到均匀

光栅之后,使用线性切趾方法完成整体优化过程。得到在 500nm 最小线宽条件下,光栅仿真峰值耦合效率为-3.7dB,仿真结果如图 3.15 所示。

图 3.15 500 nm 最小线宽灰度刻蚀切趾铌酸锂光栅设计仿真结果

#### 3.2.2 测试结果

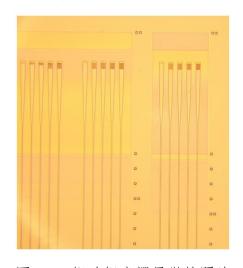

C 波段铌酸锂光栅在实验室的 LNOI 晶圆上完成实验制作,为保证制作器件的稳定制造,初步优先制作 500nm 最小线宽的铌酸锂光栅设计的器件。同时制作得到不考虑工艺问题以及考虑工艺问题优化的铌酸锂光栅,图 3.16 中展示了制作得到的光栅样品。制作过程中,由于工艺制作能力最小线宽的限制,在设置的用于线宽误差补偿实验的实验参数变化组中,每组制作光栅的刻蚀槽宽度较小的实验补偿光栅设计超出了工艺制作能力,因而没有得到相应的制作结果。表现在显微镜下,出现没有光栅图形的宽波导区域。由灰度刻蚀形成的不同厚度的铌酸锂层在显微镜下的光栅 taper 区域出现颜色上的微小变化。每组光栅旁边的标记用于灰度刻蚀在不同区域的曝光剂量标定。

图 3.16 铌酸锂光栅显微镜照片

首先对不考虑波导缩窄问题的铌酸锂光栅实验组进行测试,在 14 度光纤倾角条件下,测试得到的结果如图 3.17 所示。比例补偿实验组是用于将光栅设计的整体刻蚀槽宽按比例进行缩放,补偿制作过程中带来的线宽偏差问题。得到的铌酸锂光栅测试结果中可以看出,实际测试得到的传输曲线中心波长,在与设计相同的光纤倾角下,远远偏离了 1550nm 的设计值。而且光栅传输曲线的峰值耦合效率在测试波长区间内也相对较低,仅在 120%的刻蚀槽宽度线宽比例补偿组中,获得损耗 16dB 的铌酸锂光栅测试结果。通过测试结果可以看出,在不考虑工艺中的波导缩窄问题时,制作光栅远远偏离了仿真设计光栅结果。

图 3.17 不考虑波导缩窄的铌酸锂光栅测试结果

后续继续对考虑波导缩窄情况下的铌酸锂光栅进行测试,在 16 度光纤倾角的平面光纤测试条件下,得到光栅耦合器的测试结果如图 3.18 和图 3.19 所示。其中的定值补偿实验组是光栅刻蚀槽宽度按一定数值进行补偿的实验参数变化组。

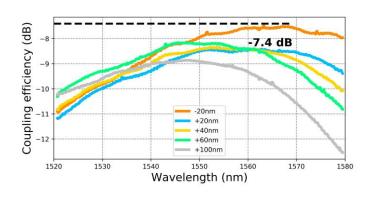

图 3.18 切趾型铌酸锂光栅线宽定值补偿组测试结果

图 3.19 切趾型铌酸锂光栅线宽比例补偿组测试结果

根据测试结果,发现分别在光栅耦合器线宽 90%比例补偿条件以及-20 nm 定值补偿条件下,取得同组光栅的最优测试值。这一测试结果说明制作过程中,光栅结构出现刻蚀槽宽度比仿真值增加的制作误差。定值补偿-20nm 的光栅设计,在 1568nm 中心波长处,测试峰值耦合效率为-7.4dB; 90%线宽比例补偿的光栅设计,在 1570nm 中心波长处,测试峰值耦合效率为-7.1dB。对于铌酸锂光栅的测试结果,相对于仿真的 3.7dB,其测试-仿真损耗偏差相对较大。后续进行实验分析,考虑主要是因为灰度刻蚀区域在较短的区域内较大的高度变化,带来灰度区域较高的传输损耗,因此出现了一定的仿真与测试之间较大的损耗偏差。制作的铌酸锂光栅在灰度刻蚀区域的显微镜放大照片如图 3.20 所示。

图 3.20 铌酸锂光栅高倍显微镜照片

图 3.20 中的制作结果可以看出,在铌酸锂光栅的灰度区域,出现了波导结构的褶皱现象,这种褶皱会以增加波导侧壁粗糙度的形式增加铌酸锂光栅 taper

区域的传输损耗。此外,在光栅密集线条结构区域,在较小线宽的补偿组中,也出现了部分光栅齿图形消失的现象,分析主要是由于显影过程中光刻胶脱落以及小线宽结构超出工艺制作能力造成的,而这种问题也一定程度上影响了光栅耦合器的测试耦合效率。

# 3.3 本章小结

本章以 C 波段光栅设计为主要内容,通过在 SOI 晶圆上结合交错刻蚀和切趾的设计结构,实现了用于商用硅光工艺的硅光栅耦合器设计。基于第二章提出的定向优化方法,完成硅光栅耦合器的切趾仿真优化,得到最终的光栅耦合器仿真耦合效率为-1.24dB。在硅光栅耦合器设计中,考虑实际制作过程中不同刻蚀深度对准误差的影响,提出了扩展光刻胶的鲁棒性版图设计,增加光栅耦合器在商用硅光工艺中不同刻蚀间的对准容差。测试得到 C 波段交错刻蚀型光栅峰值耦合效率为-2.2dB,该结果为 140nm 最小线宽下,无 SWG 结构的 220nm 顶层硅标准商用硅光工艺的硅光栅最低损耗测试结果。同时,本章也在实验室铌酸锂工艺条件下,对 C 波段铌酸锂光栅进行相应设计,在 500nm 最小线宽的设计中,得到的铌酸锂光栅最高耦合效率为-3.7dB。测试得到的 C 波段铌酸锂光栅在 500nm 最小线宽制作条件下的耦合效率为-7.1dB。

# 4 O 波段硅光栅耦合器

随着互联网时代的迅速发展,数据量的快速增长对当今的通信容量以及信息处理速度提出了更高的要求,处理高数据流量的数据中心应运而生<sup>[56]</sup>。数据中心相较于传统长距离通信应用来说,更多地在数据中心内部追求短距离高速、高质量通信。而 O 波段的无色散通信窗口,能够有效承载数据中心对通信的需求<sup>[57]</sup>。因此, O 波段相关器件的研究也随着数据中心的普及发展而增多。对于 O 波段的低损耗光栅耦合器设计,同样也需要相应的研究来解决光芯片与光纤之间的耦合问题。本章在已有的双刻蚀型高效 O 波段光栅耦合器设计方案上,开展 O 波段的光栅设计工作<sup>[30]</sup>。同时,在已有设计方案基础上,进一步探索 O 波段光栅耦合器的高耦合效率设计方案。本章主要在无其他介质材料层下,实现高耦合效率的 O 波段硅光栅耦合器仿真和测试。具体设计以商用硅光工艺为基础,进行本章节的相关设计考虑<sup>[58]</sup>。

# 4.1 双刻蚀光栅耦合器

传统单刻蚀型硅光栅耦合器仅有一个刻蚀深度作为设计结构,而且刻蚀深度还需要考虑到商用硅光代工厂的常用刻蚀工艺,一般只能在有限几个深度之间进行取值。具体到光栅耦合器的应用场景,在与单模光纤进行耦合时,常用的光栅耦合器优化过程中,切趾方法需要尽可能减小光栅前端的光栅强度,增强光纤中心位置处的光栅强度,而刻蚀深度与光栅强度直接相关。因此,在光栅耦合器设计中,多引入一个刻蚀深度,能够更好地在工艺线宽限制下,实现更优的切趾设计,充分降低光栅与光纤之间的模场失配损耗,从而提高光栅的整体耦合效率。本节以双刻蚀结构作为基础,开展双刻蚀型光栅的设计和测试工作。

# 4.1.1 双刻蚀光栅耦合器设计

硅光代工厂中的新加坡 AMF 公司工艺中常用的顶层硅刻蚀深度为 70 nm, 130 nm 和 220nm, 本节选择 70nm 和 130nm 作为单偏振双刻蚀光栅耦合器的刻蚀深度进行设计。这两个刻蚀深度的选择既可以有效实现不同刻蚀深度下光栅强度的组合,在最小线宽的限制下实现更优的切趾设计。又可以避免引入 220nm 全

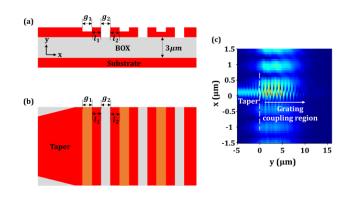

刻蚀结构带来较大泄露损耗和背反射损耗的问题。光栅耦合器在靠近 taper 区域 采用 70nm 作为刻蚀深度,实现较低的输出/输入光能量,用于拟合光纤高斯分布 前端较小的能量。在远离 taper 区域采用 130nm 刻蚀深度,实现较高的光栅强度,在光能量有一定泄露后仍能满足对应光纤位置处光能量的高斯分布。器件结构如图 4.1 所示。

图 4.1 双刻蚀光栅耦合器结构示意图

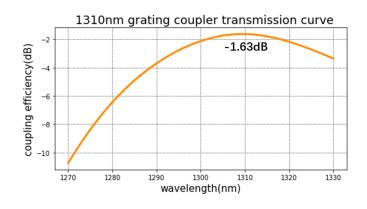

光栅耦合器的设计采用 Lumerical 的 2D-FDTD 进行仿真,仿真设计同样考虑到商用硅光工艺中的 130nm CMOS 工艺节点的最小线宽问题,设置光栅耦合器的最小线宽为 140nm,以实现在商用硅光工艺中的稳定制造。仿真过程从均匀结构出发,采用 FDTD 软件中的粒子群优化,分别优化 70nm 和 130nm 刻蚀区域内的刻蚀槽宽度和区域内光栅的周期长度,初步实现均匀双刻蚀型光栅设计。光纤倾角同样综合考虑集成度和背反射问题,选择 12°作为光纤耦合角度。仿真优化得到:在 70nm 刻蚀区域内的刻蚀槽宽度为 140nm,光栅周期为 489nm 以及 130nm 刻蚀区域内刻蚀槽宽度为 300nm,光栅周期为 556nm 时,光栅耦合器在 1310nm 波长下的仿真耦合效率为 66.67%(-1.76dB)。

在均匀双刻蚀光栅的设计基础上,采用第二章中的定向优化方法进行进一步切趾优化。在定向优化方法给定不同光栅周期的权重顺序基础上,使用 FDTD 软件中的扫描功能,对光栅不同周期内刻蚀槽宽和周期长度的结构参数进行迭代扫描。最终得到的切趾型双刻蚀光栅在 1310nm 中心波长下,峰值耦合效率为 68.72% (-1.63dB), 1dB 带宽为 30nm。图 4.2 中为切趾型双刻蚀光栅的仿真传输曲线结果。

图 4.2 切趾型双刻蚀光栅仿真传输曲线结果

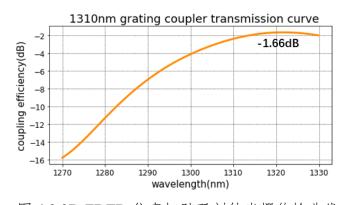

为进一步验证仿真结果,将设计好的光栅耦合器进行 3D-FDTD 仿真验证。3D-FDTD 与 2D-FDTD 最大的不同点在于: 2D-FDTD 仿真过程中,因为光栅宽度方向的 12μm 尺寸,相对于光栅耦合器另外两个维度而言,可以看作是足够大的宽度,所以在 2D 仿真的设计过程中将这一宽度方向维度简化为无穷大进行二维仿真计算。3D-FDTD 则进一步将 12μm 的宽度所在维度纳入仿真中进行模拟。此时,3D-FDTD 仿真得到光栅耦合器在 1321nm 中心波长位置处,峰值耦合效率为 68.2% (-1.66dB),图 4.3 中为切趾双刻蚀光栅的 3D-FDTD 仿真结果。

图 4.3 3D-FDTD 仿真切趾双刻蚀光栅传输曲线

图 4.3 中结果相较于 2D-FDTD 仿真可以看出,二者的耦合效率基本接近,这说明 2D-FDTD 就能得到符合仿真预期的仿真结果,只是在仿真最优值上因为计算精度有一定微小差值。而中心波长在该结构的 3D-FDTD 仿真结果中,发生了 10nm 的中心波长红移。这是由于 3D-FDTD 的光栅整体结构在宽度方向上相对 2D 仿真结构变小,使得光栅整体结构的有效折射率减小造成的结果。结合第二章中光栅方程的分析,有效折射率的减小会带来一定的中心波长红移现象。而实际测试过程中,通过增加光纤测试倾角的方式,能够有效调整实际测试结果的

中心波长,仍旧能够获得与设计中心波长相同的测试传输曲线结果。而这一问题也是光栅耦合器文章中,常见的仿真与测试之间有一定耦合倾角偏差的原因。

# 4.1.2 双刻蚀亚波长光栅耦合器设计

根据 4.1.1 节中的仿真结果,得到在 70nm 和 130nm 两种刻蚀深度下的双刻蚀型光栅设计。在这一设计的基础上,本节考虑对光栅设计进行进一步优化,尝试得到更高耦合效率的器件设计结果。在 4.1.1 节中的光栅结构,由于最小线宽的限制,在实际仿真中发现,光栅在靠近 taper 区域的刻蚀槽宽度,都取到了140nm 的线宽最小值。这一仿真结果表明:在光栅的前端部分需要比当前设计更小的光栅强度,用于减小光栅前端区域的模场失配损耗。但是在现有工艺条件下,无法进一步减小线宽得到更优的设计结果。所以,本节尝试将亚波长结构引入双刻蚀设计的刻蚀槽中,在前几个光栅周期内,结合第二章中亚波长光栅原理的理论分析,实现在光栅前端位置降低光栅强度的作用,从而在线宽受限时降低模场失配损耗。在亚波长结构的辅助下,光栅的前几个周期光栅齿区域和刻蚀槽区域的有效折射率差减小,使得原本结构中通过减小折射率差的形式实现在光栅靠近taper 区域更小的光栅强度。从而避免在使用更小刻蚀槽宽度过程中,光栅设计受到最小线宽限制的问题。图 4.4 中为亚波长双刻蚀光栅设计结构示意图。

图 4.4 亚波长辅助双刻蚀光栅设计结构示意图。(a) 结构设计剖面图。(b) 结构设计俯视图。

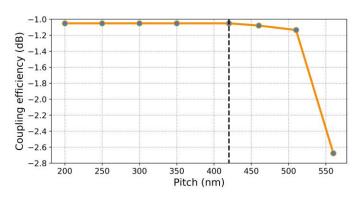

在进行亚波长辅助型光栅耦合器设计时,首先需要对亚波长光栅的周期和占 空比进行探究。通过 k 空间矢量分析及第二章中介绍的有效媒质理论, 当光栅周 期处于亚微米范围内时, 光栅耦合器可以看作是均匀的介质, 而不因为其光栅结 构产生额外的衍射效应[59]。结合亚波长相关论文中设计的结果,选取亚波长光栅 结构的周期为 420nm<sup>[31]</sup>。根据 140nm 最小线宽的限制,亚波长光栅结构的刻蚀 槽宽度和光栅齿宽度均需大于 140nm。计算得到亚波长光栅占空比因最小线宽限 制的取值范围为(140nm/420nm)33.3%~[(420nm-140nm)/420nm]66.7%。利用公式 (2-8)得到最终的亚波长光栅等效有效折射率取值区间为1.95~2.46。在这一计 算结果基础上,考虑尽可能避免工艺误差带来亚波长光栅周期长度增加,使得亚 波长光栅不满足有效媒质理论的问题,将亚波长光栅结构的周期降低为 400nm。 这样的周期长度即使在工艺中产生±20nm 的光栅周期偏移,也不会由于亚波长 结构本身产生额外的衍射效应。相应等效有效折射率区间改变为 2~2.4。在 4.1.1 节的结构设计基础上,在 2D-FDTD 中通过将亚波长光栅所在刻蚀槽设置为相应 有效折射率的介质,实现 2D-FDTD 的亚波长光栅仿真结构设置。由于光栅前端 需要尽可能小的光栅强度,所以初步在仿真中将亚波长区域的等效介质的有效折 射率设为变化区间内的最大值 2.4,以降低光栅前端的有效折射率差,实现降低 前端光栅强度的作用。以 4.1.1 节中优化得到的结构参数作为仿真基础, 进行亚 波长辅助双刻蚀光栅设计时,由于之前设计的结构参数是建立在无 SWG 结构的 前提下得到的优化参数,这导致在加入亚波长结构后,虽然以 4.1.1 中的结构参 数为优化基础能够得到一定耦合效率的设计初值,但是不能直接采取之前的参数 设计,需要对不同光栅周期内的周期长度和刻蚀槽宽度在相应结构设计下进行仿 真优化后,得到最终的优化结果。仿真过程主要对亚波长光栅所在刻蚀槽的个数 以及不同光栅周期的刻蚀槽宽度和周期长度进行优化,提高光栅的仿真耦合效率。 在亚波长光栅结构填充前5个周期刻蚀槽时,取得相应设计的最优值。后续在结 构参数优化后的基础上,通过优化亚波长光栅所在刻蚀槽的等效折射率(也就是 在计算得到的 2~2.4 有效折射率范围内取值),得到最终的亚波长辅助双刻蚀光 栅设计结果,如图 4.5 所示。

图 4.5 亚波长辅助双刻蚀切趾光栅仿真传输曲线

图 4.5 的仿真传输曲线中,在 1306nm 中心波长下,仿真得到亚波长辅助双刻蚀切趾光栅设计的峰值耦合效率为 74.6% (-1.27dB)。在此基础上,通过公式 (2-8),由仿真设计的亚波长光栅所在刻蚀槽的有效折射率推得亚波长光栅的占空比值,将相应的等效有效折射率转化为最终的亚波长光栅实际结构设计,完成光栅的整体结构设计。

# 4.1.3 测试结果

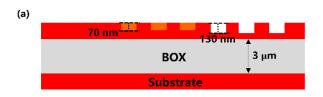

70/130nm 的 O 波段双刻蚀光栅和双刻蚀亚波长光栅设计在新加坡 AMF 工艺流片中,得到了设计器件的制造结果。在 220nm 顶层硅,3μm 埋氧层(BOX)的 SOI 晶圆上,通过 70nm 和 130nm 两种深度的刻蚀工艺,完成相应器件的制造流程,制造得到的光栅耦合器实验组样品如图 4.6 所示。

图 4.6 双刻蚀光栅及双刻蚀亚波长光栅器件显微镜结果图

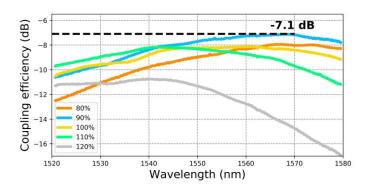

对双刻蚀光栅以及双刻蚀亚波长光栅实验组进行测试,测试得到在两种设计的线宽补偿组下的实验结果如图 4.7 所示。

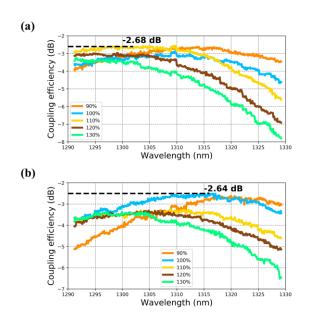

图 4.7 双刻蚀光栅及双刻蚀亚波长光栅测试结果。(a) 双刻蚀光栅测试结果。(b) 双刻蚀亚波长光栅测试结果。

实验过程中均采用 12 度光纤倾角进行测试,图 4.7 (a) 为双刻蚀光栅实验结果。其中在线宽不补偿的实验组光栅测试曲线中,测试得到在 1302nm 波长处,峰值耦合效率为-2.68dB,其他线宽补偿组均产生了一定的额外损耗和中心波长的偏移。图 4.7 (b) 为亚波长辅助双刻蚀光栅的实验测试结果,同样在线宽不补偿时,得到最优测试结果:在 1316nm 中心波长下,测试耦合效率为-2.64dB,得到的测试曲线中心波长位置附近出现相对其他波长位置较高耦合效率的小波长区间,这是因为在扫谱过程中耦合平台略微偏移了最佳耦合位置,造成除对准时的中心波长外其他区域耦合效率的相对降低。得到的测试结果中,双刻蚀亚波长光栅比双刻蚀光栅测试损耗低 0.04dB,与仿真中双刻蚀亚波长光栅与双刻蚀光栅耦合效率的仿真效率差有一定的出入。这是由于在制作过程中,未考虑滞后效应影响,带来亚波长型光栅较大的测试-仿真偏差造成的结果[46]。因此,通过进一步考虑滞后效应的影响,能够有效提升亚波长型光栅的最终测试耦合效率。

# 4.2 单刻蚀亚波长光栅耦合器

在 4.1.2 节中, 通过双刻蚀结构与亚波长光栅结构的结合, 实现了相对 4.1.1 节更高耦合效率的设计。但是多次刻蚀工艺不可避免会带来多次刻蚀对准误差以及增加制造复杂度的问题。针对这些问题, 本节考虑在单刻蚀结构上, 引入亚波

长光栅结构对光栅耦合器进行设计,尝试得到高耦合效率且只需一次刻蚀完成全部制造流程的光栅。与此同时,在4.1节设计的基础上,进一步对单刻蚀亚波长光栅耦合器进行结构以及方法上的优化,考虑滞后效应的影响,设计更高耦合效率且贴合实验结果的光栅耦合器。

# 4.2.1 单刻蚀亚波长光栅耦合器设计

对于单刻蚀型亚波长光栅结构,刻蚀深度的选择同样以商用硅光工艺中常用 的刻蚀深度为准,采用 130mm 深度的单刻蚀结构作为设计的基础。在考虑刻蚀 深度的过程中, 另外的商用硅光工艺中常用刻蚀深度 220nm 全刻蚀结构, 会引 入较大的衬底泄露损耗。因此在单刻蚀结构中,全刻蚀设计会限制光栅的最终耦 合效率。70nm 刻蚀深度虽然具有更小的泄露损耗,但是在切趾设计中,靠近光 纤中心位置处,需要相对浅刻蚀结构更高的光栅强度,而这种更高的光栅强度, 无法通过亚波长光栅结构实现降低光栅强度的作用;同时在切趾过程中,通过其 他研究者文章中的分析可以看出,在刻蚀深度接近整体晶圆高度的 1/2 时,耦合 效率取得相同晶圆厚度下光栅设计的极值[42]。70nm 相对于 130nm 刻蚀深度与切 趾设计过程中刻蚀深度的最优值 110nm 之间相差较多。因此,本节设置 130nm 作为单刻蚀亚波长光栅耦合器设计的结构参数。此外,刻蚀工艺与刻蚀区域的刻 蚀角度成正相关, 较小的刻蚀结构会导致刻蚀角的减小, 从而造成刻蚀速率的减 小[60]。由于亚波长光栅结构需要两个空间维度上较小尺寸的图形设计,这会导致 在相应结构的刻蚀过程中引入滞后效应的影响[46]。根据 4.1 节中的测试结果也能 够发现,在不考虑滞后效应影响时,亚波长结构设计虽然相较于无亚波长结构光 栅有耦合效率上的略微提升,但是显然提升幅度不满足仿真预期。因此在本节的 设计中,将滞后效应影响体现在仿真设计里,也就是设置亚波长光栅所在刻蚀槽 的刻蚀深度相对其他结构的刻蚀深度减小。根据实验中的垂直剖面 SEM 分析, 得到亚波长结构区域的刻蚀深度在 106~115nm 范围内变化,考虑到工艺测量过 程中的误差, 本节在仿真中将亚波长区域的刻蚀深度设置为测量得到的中间值 110nm, 充分拟合由于滞后效应影响带来的刻蚀深度减小问题, 光栅耦合器的设 计结构如图 4.8 所示。

图 4.8 130nm 单刻蚀光栅结构示意图。(a) 结构设计剖面图。(b) 结构设计俯视图。

光栅耦合器的设计从均匀结构出发,与 4.1 节中仿真过程相似,同样设置起始的亚波长光栅区域等效介质的有效折射率为 2.4,首先在 Lumerical 的 FDTD 中通过粒子群方法仿真优化亚波长光栅所在刻蚀槽的个数,整体光栅的周期及占空比。在亚波长光栅所在刻蚀槽的个数为 4 个时,得到仿真设计的最优值。随后,引入定向优化方法和粒子群优化方法,对光栅的不同亚波长光栅所在刻蚀槽的等效折射率,不同光栅的周期长度和刻蚀槽宽进行切趾设计。在仿真过程中,同样通过第二章中的定向优化方法,在给定的权重顺序下确定优化方向。在相应优化方向下,通过以 4 个优化参数为一组的形式,进行粒子群优化仿真迭代。最终在图 4.9 中得到在 1309nm 中心波长下,仿真耦合效率为-1.0dB 的仿真结果。

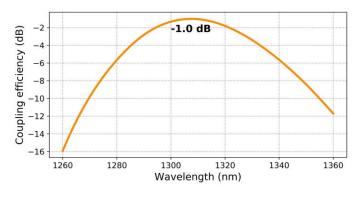

图 4.9 130nm 单刻蚀亚波长光栅仿真传输曲线

为验证亚波长结构周期长度设计的准确性,本节在单刻蚀亚波长光栅仿真结果基础上,对亚波长结构辅助光栅设计进行 3D-FDTD 仿真验证。在设计得到的结构基础上,通过扫描变化亚波长光栅的周期长度,确定亚波长光栅周期是否能符合 2D 仿真中亚波长光栅的引入未因该结构产生额外衍射,带来损耗降低的设置。仿真选择亚波长光栅周期在 200nm 到 560nm 区间内变化,得到对 130nm 单刻蚀亚波长辅助光栅的仿真结果如图 4.10 所示。当亚波长光栅在 200-420nm 周期内,3D 仿真设计结果相同。也即是说,在小于 420nm 周期长度的亚波长光栅中,不会由于亚波长光栅结构本身产生额外的衍射作用。只是作为某一折射率的介质存在,与仿真设计预期结果相符。所以选择 400nm 作为亚波长光栅的周期是可行的。这一周期的取值既可以在线宽约束下,尽可能扩展等效有效折射率的取值区间,又可以保证在一定的工艺误差下,不因工艺偏差带来亚波长结构额外的损耗。

图 4.10 3D-FDTD 仿真亚波长光栅周期对光栅耦合器效率影响

# 4.2.2 有效媒质理论的修正

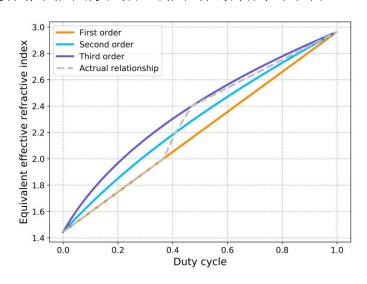

在采用与 4.1 节相同的设计过程进行仿真优化时发现: 4.2.1 节设计的 3D-FDTD 耦合效率与 2D-FDTD 仿真之差相较于 4.1.2 节中亚波长设计更为显著。分析对比两种设计的区别,发现在 4.1.2 节的双刻蚀亚波长光栅中较多的亚波长光栅区域取得接近 2.2 这一等效折射率值,而本节设计的光栅亚波长等效折射率较多的取得接近 2.4 这一等效折射率值。结合文章中常用的 EMT 分析,发现有两种 EMT 形式,分别为一阶和二阶 EMT。而两种 EMT 分析下,均无法得到与4.1 节中 2D 与 3D 仿真差值相近的本节设计的 3D 仿真结果。在此基础上,本节

尝试引入三阶 EMT 一起进行分析,三种 EMT 公式如(4-1)所示。由于设计以TE 模式单偏振光栅耦合器作为主要目标,故 EMT 均取适用于 TE 模式的公式:

$$\begin{cases} n_{eff} = (1-f) \cdot n_0 + f \cdot n_{gc} & \text{first order} \\ n_{eff}^2 = (1-f) \cdot n_0^2 + f \cdot n_{gc}^2 & \text{second order} \\ n_{eff}^3 = (1-f) \cdot n_0^3 + f \cdot n_{gc}^3 & \text{third order} \end{cases}$$

(4-1)

根据不同的 EMT 公式,对设计的单刻蚀亚波长光栅进行计算时,发现在亚波长光栅的等效有效折射率越低时,对应一阶 EMT 拟合效果越好,当仿真得到的亚波长光栅有效折射率均为 2 时,在一阶 EMT 关系得到的亚波长结构下,单刻蚀亚波长光栅的 3D-FDTD 仿真耦合效率最高。等效折射率均为 2.2 时,二阶 EMT 关系对应单刻蚀亚波长光栅的 3D-FDTD 仿真效果最优。等效有效折射率均为 2.4 时,对应三阶 EMT 拟合效果更佳。所以将这三个等效折射率值作为三个特征值进行后续分析。根据 EMT 公式和仿真模拟结果,将与 2D 仿真中亚波长区域等效有效折射率拟合效果最佳的拟合折线同样表示在图 4.11 中。

图 4.11 不同阶数 EMT 公式及仿真得到的拟合曲线

结合图 4.11 的曲线结果,可以看到在相应的 3 个特征有效折射率(2,2.2,2.4)下,分别对应不同阶数 EMT 公式的拟合效果最佳。当刻蚀槽的有效折射率分别为 2,2.2,2.4 三个等效有效折射率时,分别在一阶,二阶和三阶 EMT 下拟合效果达到最优值。因此,在实际设计中,由于实际仿真区间在 2-2.4 的折射率范围内取值,所以在相应的折射率区间内采用三个特征值作为权重,在不同等效折射率下,采用相邻特征有效折射率加权平均数的方式,得到最终对应不同等效折射率

的实际结构占空比,也就是图 4.9 中的虚线部分的占空比与等效有效折射率的关系。

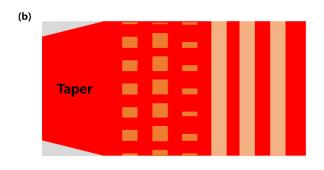

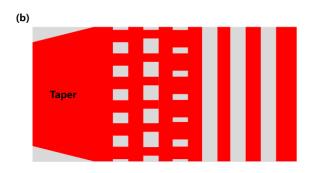

### 4.2.3 单刻蚀梯形亚波长光栅耦合器设计

在单刻蚀亚波长光栅设计以及有效媒质理论修正的基础上,本节继续更深入地考虑亚波长光栅在低损耗光栅耦合器中的作用。在光栅耦合器的前端,SWG结构降低了由光栅结构带来的光栅齿与刻蚀槽间的有效折射率差。但是值得注意的是,虽然这种结构使得刻蚀槽和光栅齿间有效折射率的变化幅度减小,但是在刻蚀槽与光栅齿的界面处仍旧存在有效折射率的突变问题,这种折射率突变会在界面处带来一定的不可控泄露损耗。因此本节提出了一种新型的低损耗亚波长光栅设计方案,通过对亚波长光栅进行结构设计,实现设计所在的刻蚀槽内的折射率渐变,进一步降低由于界面处折射率突变带来的泄露损耗影响。具体到设计结构中,将亚波长光栅设计成图 4.12 中的形式。

图 4.12 单刻蚀梯形结构亚波长光栅设计示意图 (a) 光栅设计剖面图 (b) 光栅设计平面图

图 4.12 中 (a) 为梯形结构设计的剖面图, (b) 为相应设计的平面图。通过梯形亚波长光栅结构,能够在图 (a) 剖面图的亚波长光栅所在刻蚀槽内沿 taper 指向光栅耦合区域的等效折射率实现线性的渐变过程,进而实现相应的仿真结果。仿真过程与 4.2 节前述的单刻蚀亚波长光栅耦合器相同,而对于这种线性变化的

亚波长光栅结构,在 2D-FDTD 仿真中将其所在的刻蚀槽,划分为 10 个相同宽度的区间,每个区间根据整个刻蚀槽内的线性折射率变化关系,在全部 10 个区间内取值设置相应的材料等效折射率。该仿真设置如图 4.13 所示。

图 4.13 线性亚波长光栅仿真设置示意图

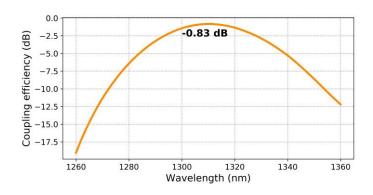

在每个划分的十个相等宽度的区间内, 对每个梯形亚波长结构, 设置起始折 射率和终止折射率,这两个参量分别对应线性亚波长结构所在刻蚀槽两端位置划 分区间的有效折射率起始变化值。中间的其他划分区间,按照线性变化关系,得 到相应的有效折射率值。在仿真优化过程中,首先将线性亚波长光栅设置为较大 的折射率, 起始折射率与终止折射率均设置为 2.4。随后, 在粒子群优化中, 同 时优化亚波长光栅区域的起始折射率,终止折射率,光栅周期长度和光栅刻蚀槽 宽度,在亚波长光栅所在刻蚀槽个数为9个时该设计的仿真得到最优值。这时每 个梯形亚波长光栅的起始等效折射率为 2.4,终止等效折射率为 2.25。以此作为 优化基础,切趾仿真优化不同光栅周期内:光栅长度,刻蚀槽宽度,梯形光栅的 起始等效折射率和终止等效折射率,得到最终的优化结果。得到的最优设计结果 中可以发现,在光栅初端两个光栅周期内,梯形亚波长结构的终止和起始等效折 射率均取最大值 2.4 时,取得仿真最优值。说明光栅初端追求的更多还是以对光 栅强度的减小,实现模场失配损耗的降低为主的设计。在后面的亚波长光栅区域 内, 部分亚波长光栅优化取得梯形亚波长设计结构, 在仿真中, 相对 4.2.1 节中 的设计体现出了梯形亚波长结构对于仿真耦合效率的提高作用。得到最终的光栅 耦合器在 1309nm 中心波长下,仿真峰值耦合效率为-0.83dB,在图 4.14 中为该 仿真结果的传输曲线。

图 4.14 单刻蚀梯形亚波长光栅设计仿真传输曲线

该仿真结果相较于 4.2.1 中的设计,有了进一步耦合效率上的提升,通过梯 形亚波长光栅的设计,在仿真上有效证明了线性渐变想法的可行性,体现在具体 设计中,对于光栅耦合器的仿真耦合效率具有 0.17dB 的提升作用。

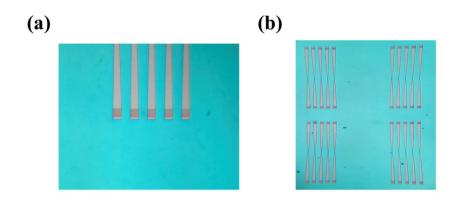

### 4.2.4 测试结果

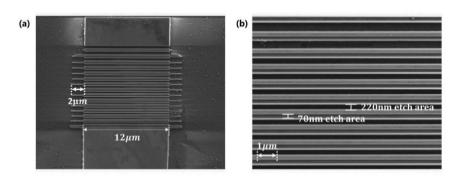

O 波段的 130nm 单刻蚀亚波长光栅和梯形亚波长光栅设计,在上海高研院的工艺平台上完成制造。在标准 220nm 顶层硅的 SOI 晶圆上,通过电子束曝光,完成光栅整体结构的光刻胶掩膜,最终在 ICP 工艺中完成对顶层硅图形的刻蚀制作。制作得到的器件如图 4.15 所示。

图 4.15 130nm 单刻蚀切趾型光栅显微镜照片。(a) 局部放大显微镜图。(b) 整体光栅结构显微镜图

图 4.15 (a) 为光栅样品的局部放大显微镜照片, (b) 则是光栅样品整体结构的显微镜照片。在前三批制造得到的光栅样品中,通过台阶仪测试,得到实际制作样品光栅区域的刻蚀深度均偏离设计的 130nm 刻蚀深度。每批次光栅器件样品测试得到的结果如图 4.16 所示。其中图 (a),图 (b) 和图 (c) 为实际刻蚀

深度 95nm 的器件测试结果。由于刻蚀深度相对设计值偏差较多,调整光纤角度为 20 度对所有光栅进行测试。图 (a) 为 130nm 单刻蚀常规亚波长切趾光栅设计线宽比例补偿组,当刻蚀槽宽的线宽进行 120%比例补偿时,在 1300nm 中心波长下,测得峰值耦合效率为-3.5dB。图 (b) 为 130nm 单刻蚀亚波长切趾光栅设计线宽定值补偿组,在线宽进行+10nm 补偿时,在 1298nm 中心波长处的测试耦合效率为-3.0dB。图 (c) 为 130nm 单刻蚀梯形亚波长切趾光栅设计线宽比例

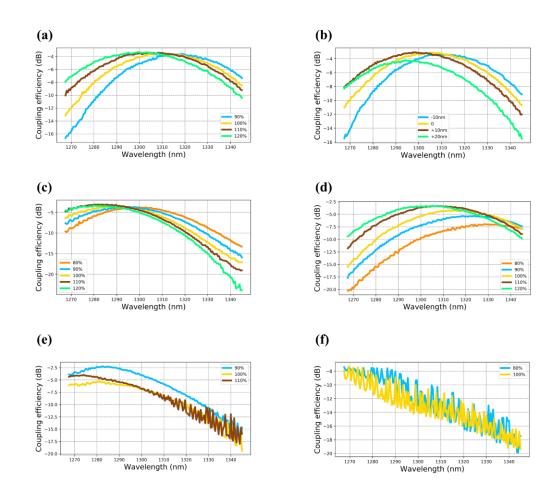

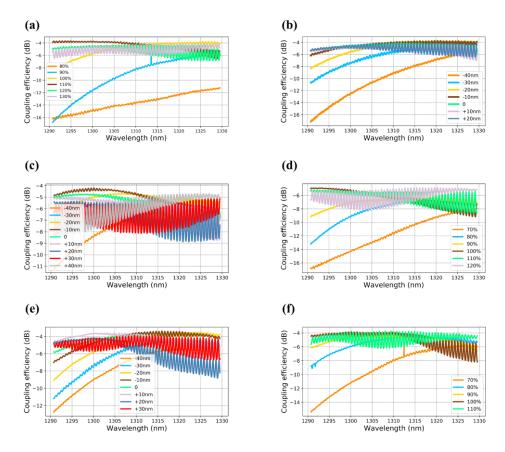

图 4.16 单刻蚀亚波长光栅耦合器测试结果。95nm 刻蚀深度制作样品的(a) 130nm 单刻蚀常规亚波长光栅比例补偿实验组和(b)定值补偿组以及(c) 130nm 单刻蚀梯形亚波长光栅比例补偿组。110nm 刻蚀深度制作样品的(d) 130nm 单刻蚀常规亚波长光栅比例补偿组。160nm 刻蚀深度制作样品的(e) 130nm 单刻蚀常规亚波长光栅比例补偿组和(f)130nm 单刻蚀梯形亚波长光栅比例补偿组

补偿组,测得 110%刻蚀槽宽线宽补偿光栅在 1284nm 中心波长处,峰值耦合效率为-3.0dB。图(d)为刻蚀深度 110nm 的制造器件测试结果,由于 110nm 刻蚀深度的制造过程中,在制作过程中出现较多的图形畸变现象,所以仅测试了130nm 单刻蚀亚波长切趾光栅的比例补偿组。在线宽比例补偿 120%时,测试最优峰值耦合效率为-3.3dB。图(e)和图(f)则是第三次制作得到的 160nm 刻蚀深度的器件测试结果,光纤测试角度调整为 12 度,与仿真光纤耦合角度 14 度相近。其中,图(e)为 130nm 单刻蚀常规亚波长切趾光栅设计的比例补偿组,在刻蚀槽线宽比例补偿 90%时,测得 1284nm 处峰值耦合效率为-2.2dB,而图(f)中则是梯形亚波长光栅在 8 度光纤倾角时的测试结果,可以看出中心波长在 8 度倾角时也仍旧小于 1270nm,峰值耦合效率更是高于-8dB,远远偏离仿真预期值。而这一结果也是由于梯形亚波长结构在本批次制作中出现图形畸变以及刻蚀深度偏移造成的。

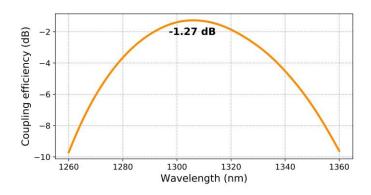

在之前工艺的基础上,通过调整曝光剂量以及后续的重复试验,最终得到刻蚀深度为 130nm 的实验样品。本批次样品相较于之前的制作结果,具有更好的图形线条制作情况,未出现图形畸变现象。对最终制造得到的光栅器件进行测试,测试光纤采用 14 度倾角,得到 130nm 单刻蚀亚波长切趾光栅以及 130nm 单刻蚀梯形亚波长切趾光栅的测试结果在下图 4.17 中。

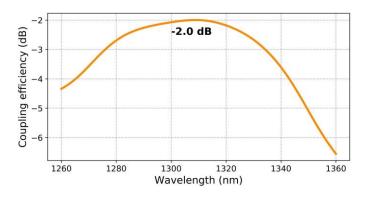

图 4.17 130nm 单刻蚀亚波长光栅及梯形亚波长光栅设计最终测试结果

图 4.17 的两个结果均是在线宽未进行补偿条件下测试得到的。其中,梯形亚波长光栅在 1295nm 中心波长下,测试耦合效率为-1.73dB。常规结构的亚波长光栅在 1310nm 中心波长出,测试峰值耦合效率为-1.93dB。这两个测试结果符合仿真结果预期,而梯形亚波长光栅发生相较于 1310nm 波长的一定中心波长偏移,是由于仿真过程中梯形亚波长设计与常规亚波长设计存在 3 度的光纤倾角之差

造成的。而测试过程中由于测试光纤倾角未改变,所以产生了一定的中心波长偏移。这两组测试结果得到的光栅设计,在 O 波段只需一次简单的单刻蚀工艺完成制造,据作者所知,根据第一章表 1-1 的结果对比,本章设计得到了同类光栅的最低损耗结果。

# 4.3 双向渐变亚波长光栅耦合器

在 4.2 节中, 通过梯形亚波长光栅结构设计, 能够在光传播方向的刻蚀槽内实现折射率的线性渐变, 有效降低由于折射率突变带来的损耗问题。在这一想法的基础上, 继续考虑将渐变的概念引入光栅刻蚀槽的两端, 进一步降低由折射率突变带来的泄露损耗问题。

# 4.3.1 双向渐变亚波长光栅耦合器设计

根据折射率渐变的设计思想,在对亚波长结构所在的刻蚀槽内,可以不止在一端实现折射率渐变,在刻蚀槽两端的区域可以均设计有折射率渐变效果的结构。基于这样的想法,本节提出了六边形和圆角矩形的亚波长光栅结构,用于实现双向折射率渐变设计。在图 4.18 展示了对应的两种设计结构。

图 4.18 圆角矩形和六边形亚波长光栅结构辅助单刻蚀光栅示意图。(a) 圆角矩形亚波长结构设计剖面图。(b) 六边形亚波长结构设计剖面图。(c) 圆角矩形亚波长结构设计平面图。(d) 六边形亚波长结构设计平面图。

在图 4.18 中, (a) 和 (c) 分别表示圆角矩形亚波长光栅设计的剖面图和平面图, (b) 和 (d) 分别指的是六边形亚波长光栅设计的剖面图和平面图。六边

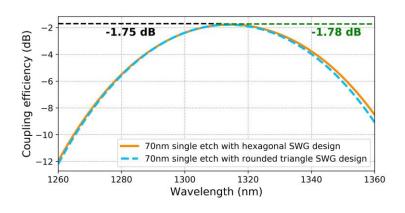

形亚波长光栅结构可以在光栅刻蚀槽两端到中间位置的变化过程中,实现光传播方向的线性折射率渐变。而圆角矩形亚波长结构,则能够实现抛物线型折射率渐变。在这两种结构设计想法下,尝试使用硅光工艺中的另一个常用刻蚀深度 70nm进行设计。在 70nm 刻蚀深度下,由于常规均匀光栅损耗较小,在进行后续新型结构的均匀设计与均匀光栅实验对比中,能够更好地说明设计的效果,排除因均匀光栅在相应刻蚀深度下损耗较大的问题影响。仿真过程与梯形亚波长光栅耦合器相同,区别在于对亚波长结构所在区间内的等效折射率变化趋势不同。此时,在这两种结构下,在每个亚波长结构所在的刻蚀槽内,圆角矩形和六边形亚波长结构分别进行等效折射率的抛物线型和线性变化,得到相应区间内的介质有效折射率值。仿真优化亚波长光栅所在刻蚀槽个数,亚波长结构的起始等效折射率和截止等效折射率值以及整体光栅周期长度和占空比大小,在亚波长光栅为 5 个,起始等效折射率为 2.4,截止等效折射率值为 2.24 时,分别得到六边形和圆角矩形亚波长结构设计下的均匀型光栅耦合器的仿真结果,如图 4.19 所示。

图 4.19 六边形和圆角矩形亚波长光栅辅助均匀光栅仿真传输曲线

此时,在图 4.19 中,得到圆角矩形亚波长光栅设计在 1313nm 中心波长处,耦合效率为-1.75dB;而六边形亚波长光栅设计在 1314nm 中心波长处,耦合效率为-1.78dB。该两种设计仅在均匀条件下完成仿真,未进一步引入切趾对光栅设计完成优化。尝试与普通均匀光栅进行实际制作对比,得到器件制作结果。

#### 4.3.2 测试结果

O 波段 70nm 均匀型的六边形和圆角矩形亚波长光栅设计在新加坡 AMF 代工厂完成相应的制作工艺。整体器件只需 70nm 刻蚀即可完成全部的制造流程。制作得到的光栅耦合器如图 4.20 所示。

图 4.20. 六边形及圆角矩形亚波长光栅辅助单刻蚀光栅器件显微镜图

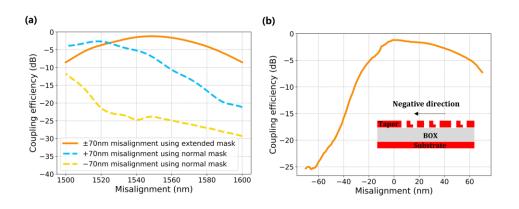

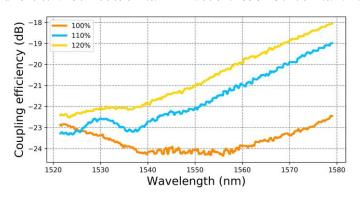

对制作得到的器件进行测试,分别测试六边形,圆角矩形亚波长辅助单刻蚀 光栅以及相同工艺下均匀光栅实验参数变化组的传输曲线,相应的测试结果如图 4.21 所示。

图 4.21.70nm 均匀型六边形和圆角矩形亚波长光栅设计测试结果。(a) 单刻蚀均匀光栅比例补偿组。(b) 圆角矩形亚波长光栅比例补偿组。(c) 六边形亚波长光栅比例补偿组。(d) 最优测试结果对比。

图 4.21 中, (a) 图为相同工艺制作条件的 70nm 单刻蚀均匀光栅的比例补偿组测试结果,该测试结果用于与两种提出的亚波长光栅结构进行对比,证明两种

亚波长光栅结构相较于常规均匀光栅对耦合效率的提升效果。(b) 图为圆角矩形亚波长光栅的比例补偿测试结果,其中得到在 120%线宽补偿条件下,光栅的测试耦合效率最高。(c) 图为六边形亚波长光栅的比例补偿实验组测试结果,在 120%线宽比例补偿条件下,得到同组最高耦合效率测试结果。在 (d) 图中,将两种亚波长光栅的最优测试结果,与相同线宽补偿条件的均匀光栅进行对比,可以从结果中看出:测试得到的均匀型光栅,在六边形亚波长结构设计条件下,测试得到峰值耦合效率为 1303nm 波长的-2.95dB; 在圆角矩形亚波长条件下,测试峰值耦合效率为-3.3dB。相同工艺条件的均匀光栅,在 1309nm 中心波长下,测试峰值耦合效率为-4.15dB。通过测试结果对比可以看出,提出的两种新型亚波长光栅设计相较于相同工艺条件的普通均匀光栅,能够在六边形和圆角矩形亚波长结构中分别提高耦合效率 1.2dB 和 0.85dB。六边形和圆角矩形亚波长结构之间的耦合效率差,则主要是由于设计过程中,在划分亚波长光栅的区间时,均采用均分的方式进行。这样的仿真模拟更贴合线性折射率渐变的变化趋势,也就是六边形亚波长结构设计。因此,得到的六边形亚波长光栅耦合效率相对圆角矩形亚波长结构较高。

# 4.4 本章小结

本章在 O 波段的硅光栅设计结构中,通过结合 O 波段的双刻蚀高耦合效率设计方案以及第二章中的亚波长光栅原理,实现 O 波段的硅光栅器件设计。2D-FDTD 仿真设计了 70/130nm 双刻蚀型光栅耦合器,在 1310nm 波长下,仿真峰值耦合效率为-1.63dB。结合亚波长光栅与双刻蚀光栅设计,仿真得到峰值耦合效率在 1306nm 波长处为-1.26dB。考虑对光栅制造工艺的进一步简化,设计了130nm 单刻蚀光栅耦合器,结合滞后效应及修正的亚波长光栅原理,仿真在1309nm 中心波长处,耦合效率为-1.0dB。本章提出了折射率渐变的新型梯形亚波长光栅结构,在 130nm 单刻蚀制作条件下,仿真得到峰值耦合效率为 O 波段下的-0.83dB。测试得到世界最低损耗无金属反射镜和底部分布式反射镜的 O 波段梯形亚波长结构单刻蚀光栅,测试结果为-1.73dB。基于折射率渐变的想法,进一步提出新型六边形及圆角矩形亚波长光栅结构,在 70nm 单刻蚀制作条件下,均匀光栅的仿真峰值耦合效率分别为-1.78dB 和-1.75dB。这两种设计结构由于希

望用于与均匀光栅进行对比说明对于损耗的降低作用,故未进行后续的切趾仿真优化。测试得到相较于相同工艺条件均匀光栅的-4.15dB,分别提升 1.3dB 和 0.85dB 的测试耦合效率。

# 5 硅-氮化硅多层光栅耦合器

传统光栅在单层硅光栅结构中,考虑商用硅光工艺的刻蚀深度和最小线宽等限制,存在模场失配损耗未完全补偿以及泄露损耗较大的问题。这些问题导致耦合效率在单层硅光栅结构上无法进一步提升。本章提出了一种高效宽带光栅耦合器设计,能够兼容氮化硅材料的带宽特性以及提升光栅的耦合效率。考虑到商用硅光代工厂的可行工艺,将氮化硅层设计成为增透膜的形式,在商用硅光工艺中,通过氮化硅层与硅层共同作用实现最终的多层光栅耦合器设计。在 AMF 的氮化硅工艺条件下,设计了硅-氮化硅双层高耦合效率光栅以及硅-双氮化硅的三层高耦合效率光栅。

# 5.1 一种高效宽带光栅耦合器设计

提高光栅耦合器耦合效率性能的传统方式,主要是通过金属反射镜和底部多层介质的分布式反射镜实现。而这两种结构在第一章中也阐明了工艺实现上的困难。所以,结合实际可用的硅光 CMOS 兼容工艺,考虑在硅层上方通过淀积形成多层氮化硅结构,实现耦合效率的提升。此外,氮化硅结构除了是商用硅光工艺中的常见工艺结构外,相较于硅光栅,其材料组成的光栅带宽更大。光栅耦合器件的 1dB 带宽可以通过如下公式进行计算[61]:

$$BW_{1dB} = \eta_{1dB} \frac{\lambda_0 n_{SiO_2} \cos \theta}{n_{eff} - n_{SiO_2} \cos \theta}$$

(5-1)

其中,η<sub>1dB</sub>是由光栅的结构参数决定的参量。在相同结构下,氮化硅材料光栅相较于硅材料光栅,光栅的有效折射率更小,根据(5-1)所示,计算得到的 1dB 带宽更大。基于光栅带宽的公式分析,考虑将氮化硅材料作为光栅结构的光传输层。但是,氮化硅材料光栅的常规全刻蚀工艺及与包层较小的折射率差带来的泄露损耗问题,需要进一步解决。本节考虑在氮化硅层下方,淀积一系列氮化硅形成 DBR 结构,与 SOI 晶圆的顶层硅共同反射泄露损耗,形成整体的高耦合效率设计<sup>[62]</sup>。具体结构设计如图 5.1 所示。

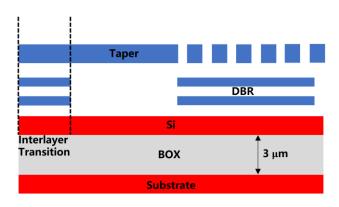

图 5.1 高效宽带光栅耦合器二维结构示意图

通过图 5.1 中的设计结构,能够有效与 220nm 顶层硅器件兼容。只需在硅层和最上层氮化硅之间设计层间耦合结构,就能完成从硅层到氮化硅层的光能量传输。此时,中间层的氮化硅结构,也能够实现对顶层硅和最上层氮化硅距离较远时的光能量过渡作用。在这一结构的构想下,采用 2D-FDTD 对该设计的均匀结构进行仿真。仿真得到在顶层氮化硅厚度 450nm,硅层到最下层氮化硅间距420nm,中间淀积四层氮化硅材料且厚度均为 150nm 以及顶部氮化硅到硅层间距2.23μm 时,仿真峰值耦合效率为 1309nm 波长的-2.0dB,仿真结果在图 5.2 中体现。

图 5.2 均匀型高效宽带光栅耦合器设计仿真传输曲线

该仿真结果中,得到均匀结构的氮化硅光栅设计,能够具有-2.0dB的耦合效率,与其他氮化硅光栅相比,该仿真结果的耦合效率较高。同时,器件的1dB带宽接近60nm,远高于传统硅光栅耦合器的带宽。可见,这种结构具有实现高效宽带特性的潜力。但是由于实际制造过程较为复杂,该结构仅作为专利形式发表,未进行后续的实验和测试工作。

### 5.2 硅-氮化硅光栅耦合器

在 5.1 节设计中,虽然使用硅-氮化硅结构有效打破垂光栅结构直方向的对称性,提高光栅的耦合效率。同时利用氮化硅材料的带宽特性,整体提升了光栅耦合器设计的性能。但是,无论是额外的层间耦合结构,还是工艺复杂度上,都使得相应设计有一定的限制。目前主流的研究仍旧需要以氮化硅材料作为光传输层进行多层光栅设计,通过垂直方向上的硅-氮化硅结构形成复合模式,提升耦合效率。但是这种结构需要较近的硅-氮化硅间距,在硅-氮化硅间距较远时耦合效率受限。仅有 Luxtera 在 2020 年采用硅层作为与波导相连的光传输层,仿真设计了高耦合效率的硅-氮化硅双层光栅耦合器<sup>[63]</sup>。与该工作设计想法相似,本节尝试采用硅-氮化硅双层光栅设计,同样通过将硅层光栅作为与波导相连的传输层,减小由于氮化硅双层光栅设计,同样通过将硅层光栅作为与波导相连的传输层,减小由于氮化硅对层光栅设计。此外,氮化硅层作为增透膜的形式,采用商用硅光工艺中的工艺流程,即可完成相应的制造工作,充分简化制造流程及增强结构的工艺可实现性。

# 5.2.1 氮化硅参数的确定

对于硅-氮化硅双层光栅耦合器结构,在硅层高耦合效率设计结构之外,需要考虑到氮化硅层在光栅整体设计中的作用。由于商用硅光工艺中,氮化硅层在220nm 顶层硅的 SOI 晶圆上方一定距离的位置进行制造,而这种一定距离的介质层结构,在光学中参照光学透镜增透膜的设计思想,通过设计氮化硅层作为光栅的增透膜结构能够有效结合氮化硅层实现高耦合效率光栅的设计。所以氮化硅层的作用考虑设计成为增透膜的形式,增强光栅的整体耦合效率[64]。增透膜的原理如公式(5-2)所示。

$$2n_2d = (2k+1)\frac{\lambda}{2}$$

$k = 0,1,2\cdots$  (5-2)

在公式中, n<sub>2</sub>表示增透膜结构使用材料的有效折射率, d 表示增透膜与光传输层的间距。具体到本节的结构设计中, 将氮化硅层作为一层增透膜结构, 尝试得到相应的仿真结果。在硅-氮化硅双层光栅设计过程中, 需要进一步考虑工艺

上的可行性问题。同样以 AMF 工艺作为设计基础,进行相应的硅-氮化硅双层光栅耦合器设计。由于实际应用在大规模光开关阵列项目的需要,应尽可能考虑与光开关阵列输入端模斑转换器以及光开关阵列路由过程中的交叉波导性能,确定氮化硅层参数(包括氮化硅层到硅层的间距以及氮化硅层的厚度)<sup>[65]</sup>。经过与组内其他同学的合作,综合考虑三种器件的性能,最终得到了氮化硅层的相关工艺参数,如图 5.3 所示。

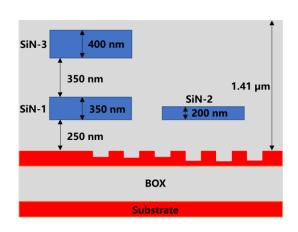

图 5.3 多层氮化硅结构参数示意图

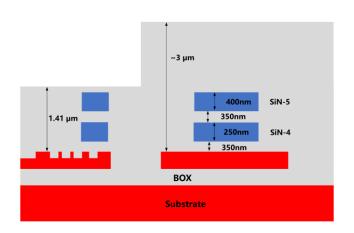

在得到的氮化硅参数中,主要有三层氮化硅结构。下层氮化硅 SiN-1 厚度 350nm,距离顶层硅间距 250nm。在整体下层氮化硅的结构基础上,加入一层用于氮化硅层的 150nm 浅刻蚀工艺,能够形成较薄的 200nm 氮化硅层 SiN-2 结构,距离顶层硅间距同样为 250nm。上层氮化硅 SiN-3 厚度 400nm,距离顶层硅间距 为 950nm。

### 5.2.2 硅光栅-氮化硅增透膜结构设计

在进行硅-氮化硅增透膜结构双层光栅设计时,以第四章中设计作为硅层的设计结构。在原本较高耦合效率的结构基础上,引入氮化硅层,得到最终的设计结果。此时,整个光栅器件所需的工艺相对简单,只需在顶层硅引入 130nm 单刻蚀,后续在顶层硅上方化学气相淀积形成一定厚度的二氧化硅和氮化硅层,即可完成整体的制造流程。

由于氮化硅层参数固定,无需进行额外优化,但氮化硅层的引入,会影响原本硅层高耦合效率结构的建设性干涉条件。故需在相应的氮化硅层参数下,将硅层的结构参数:硅层光栅的刻蚀槽宽,光栅周期长度以及亚波长区域的有效折射

率继续进行切趾优化,最终得到在相应氮化硅参数下的设计结果。考虑到在商用硅光工艺中,较小尺寸的特殊结构可能存在制作上的问题。所以,为保证得到实际的测试结果,采用硅层 140nm 继续作为最小线宽进行设计。本节采用与 4.2.1 中相同的设计结构作为硅层设计的优化起点,在 130nm 单刻蚀常规亚波长结构基础上进行优化设计。不选择 4.2.2 节中的设计是为了避免渐变型亚波长结构在制作过程中出现较大的制作偏差,保证相应设计能够得到稳定的制造结果。优化过程采用第二章中的定向优化方法进行,对硅层光栅结构进行权重排序,在权重由高到低的顺序下,进行硅层不同光栅周期的周期长度和刻蚀槽宽度以及亚波长光栅的等效有效折射率的切趾优化。在该设计条件下,亚波长光栅所在刻蚀槽的个数最终优化为 8 个,光栅周期和刻蚀槽宽度随着氮化硅层参数的不同而有所区别,整体均呈现非均匀的结构设计。最终,在不同的氮化硅参数下,仿真得到硅-氮化硅增透膜结构设计的结果如表 5.1 所示。

| 光栅编号 | 氮化硅层  | 仿真峰值耦<br>合效率 | 中心波长    |

|------|-------|--------------|---------|

| G1   | SiN-3 | -1.2 dB      | 1303 nm |

| G2   | SiN-1 | -0.89 dB     | 1310 nm |

| G3   | SiN-2 | -0.88 dB     | 1310 nm |

表 5.1 硅-氮化硅增透膜结构设计仿真结果

在 SiN-3 参数条件及 1303nm 中心波长下, 仿真峰值耦合效率为-1.2dB。另外两种氮化硅参数下, 350nm 厚度的氮化硅层(SiN-1) 在中心波长 1310nm 处, 仿真耦合效率为-0.89dB; 而 200nm 厚度的氮化硅层(SiN-2) 在中心波长 1310nm 处, 仿真耦合效率为-0.88dB。可以看出, 较厚且距离顶层硅较远的 SiN-3 参数, 偏离增透膜设计最优值较多, 出现了相较于硅光栅一定程度上的耦合效率劣化。而 SiN-1 和 SiN-2 结构参数,表现出相对单层硅光栅仿真耦合效率上的提升。

## 5.2.3 硅光栅-氮化硅增透膜结构设计测试结果

对仿真得到的硅光栅-氮化硅增透膜结构设计,在 AMF 进行流片实验。得到器件的制作结果如图 5.4 所示。其中的氮化硅层参数与图 5.3 中的结构参数相同, 硅层光栅通过 130nm 深度的刻蚀实现制造。

图 5.4 硅光栅-氮化硅增透膜结构样品显微镜照片

对测试得到的硅光栅-氮化硅增透膜结构样品进行相应的测试数据分析,三种氮化硅参数下的硅-氮化硅增透膜设计结构不同实验补偿组的测试结果如图 5.5 所示。得到的测试结果中可以明显看出,部分测试传输曲线的谐振现象较为明显。

图 5.5 硅光栅-氮化硅增透膜结构测试结果。SiN-1 参数 G2 光栅设计 (a) 线宽比例补偿组和 (b) 线宽定值补偿组。SiN-3 参数 G1 光栅设计 (c) 整体结构定值补偿组以及 (d) 光栅刻蚀槽宽比例补偿组。SiN-2 参数 G3 光栅设计 (e) 整体结构定值补偿组以及 (f) 光栅刻蚀槽宽比例补偿组。

在进行实验设计中,同样为了考虑尽可能在工艺参数变化的前提下,实现符 合仿真预期的实验制作结果。对不同设计的光栅进行刻蚀槽宽度的线宽比例补偿 实验组和定值补偿实验组设置。其中,当制作线宽发生偏差时,通过这些实验补 偿组,能够一定程度上消除因工艺线宽误差带来对器件性能的影响。同样在测试 过程中先在垂直耦合平台下进行三维方向的对准, 找到最佳耦合位置。随后每组 测试在 1290-1330nm 波长范围内进行,每次测试在相应测试波段内等区间选取 800 个测试数据点。在图 5.5 中,图(a)和图(b)分别为 SiN-1 氮化硅参数条 件下的硅光栅-氮化硅增透膜结构 G2 的线宽比例补偿和线宽定值补偿组测试结 果,在线宽比例 110%补偿条件下,得到该设计最高耦合效率测试结果为 1291nm 波长的-3.7dB。通过图(a)结果可以看出,在刻蚀槽线宽比例补偿 100%-120% 时, G2 光栅的峰值耦合效率变化较小, 仅在 120%补偿组中, 相对 110%补偿组 的峰值耦合效率降低 0.55dB。此外, 在线宽比例补偿组的测试结果中, 可以看出 随着刻蚀槽线宽按比例增加,光栅的中心波长不断发生红移。在图(b)的定值 补偿组中,同样随着刻蚀槽线宽按定值方式增加的过程中,光栅的中心波长进行 红移。图(c)为 SiN-3 氮化硅参数条件下的 G1 光栅设计刻蚀槽宽与亚波长光栅 的刻蚀槽宽同时进行定值补偿的实验组,得到在-10nm 线宽整体补偿时,中心波 长 1300nm 的峰值测试耦合效率为-3.2dB。同时在图(c)中,随着整体结构定值 补偿数值增加, 曲线谐振现象加剧。而这种谐振增加的现象出现在同类设计的所 有线宽增加的实验组中。这一结果分析是由于刻蚀槽宽度的增加,导致在该结构 下亚波长光栅所在的刻蚀槽宽度增加,而这种相对之前设计较大的多刻蚀孔结构, 更容易在曲线中产生明显的谐振现象。图(d)则是与图(c)相同设计下仅对刻 蚀槽宽度进行比例补偿的实验组,此时在120%线宽比例补偿条件下,得到的最 优峰值测试耦合效率为-4.4dB。通过这两组实验对比可以看出,只有当 G1 在刻 蚀槽宽与亚波长结构同时进行补偿过程中,能够获得相对其他设计较高的耦合效 率结果,图(c)在-10nm补偿组中的测试耦合效率为-3.2dB,而图(d)中与-10nm 线宽补偿相似的补偿组为 90%比例补偿,此时的测试耦合效率小于-6dB。而图(c) 和图 (d) 两组测试结果唯一区别在于是否加入亚波长光栅区域的补偿设计。所 以可以说明在当前条件下, 亚波长光栅参数不是最优值, 而这一点也是由于初次 硅-氮化硅光栅实验中, 未考虑亚波长结构带来滞后效应的影响导致的。同样依

据第四章中 4.1 节的测试结果,当不考虑亚波长滞后效应影响时,同样在 AMF 工艺条件下,仿真与制作损耗之间相差 1.3dB,造成仿真和测试之差进一步增大。而在本节中的设计,则由于原本适用于仿真设计的氮化硅结构,在硅层发生结构变化时,氮化硅层结构相当于进一步破坏了建设性干涉条件,继续恶化了整体性能。图(e)和图(f)是在 SiN-2 氮化硅参数的硅-氮化硅增透膜结构光栅 G3测试结果,同样可以在图(e)的亚波长区域和刻蚀槽宽同时补偿实验组中发现,在-10nm 补偿条件下取得最优值,可见这种设计下,需要-10nm 的整体补偿结构取得实验最优值。测试得到在 1314nm 波长的峰值耦合效率为-3.3dB。图(f)的刻蚀槽宽比例补偿组中,同样仅获得测试结果低于-4dB的测试结果。此外,参照组内同学的测试结果,在相同工艺下制作的硅-氮化硅层间耦合结构,仿真设计值为-0.02dB,而实际制作损耗为-0.14dB。这一测试结果说明氮化硅层结构参数也同样发生了漂移,同样影响了相应光栅器件的性能。

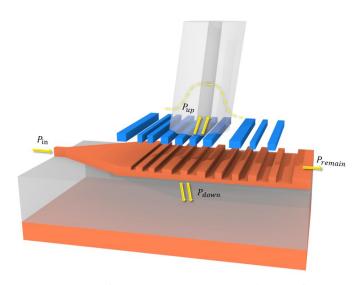

#### 5.2.4 硅-氮化硅双层切趾光栅设计

在前述 5.2.2 节中,可以发现在不同氮化硅层结构条件下,氮化硅层参数对光栅耦合器的性能有着不同程度的影响。甚至在 SiN-3 结构下,会降低光栅的整体耦合效率。分析这一问题,考虑主要是因为氮化硅参数固定,这种固定的结构导致氮化硅参数无法完全满足增透膜条件,甚至是部分满足增反膜条件出现的问题。因此,在 5.2.2 节中氮化硅层作为增透膜设计的基础上,进一步考虑将这一氮化硅层制作成光栅的结构。该想法能够在不同氮化硅到硅层间距下,通过调整光栅结构的占空比,实现对该层氮化硅整体折射率的调节,能够适应不同氮化硅厚度及氮化硅到硅间距的应用场景。具体到原理中,能够在不同的氮化硅参数条件下,通过调整氮化硅层光栅的整体有效折射率,在相应氮化硅条件下满足增透膜条件。除此之外,通过在氮化硅层同时引入切趾的概念,能够在硅层最小线宽受限的区域,通过顶部的氮化硅层切趾,调整不同垂直区域内的整体结构有效折射率,实现更优的切趾设计。硅-氮化硅双层光栅设计结构如图 5.6 所示。

图 5.6 硅-氮化硅双层切趾光栅结构示意图

由于这种设计结构需要氮化硅层的刻蚀工艺实现,考虑 AMF 的氮化硅层线 宽的工艺制作能力,将氮化硅层最小线宽设置为 250nm,最小刻蚀槽宽度为 350nm。硅层同样考虑使用第四章中的亚波长光栅设计。对硅-氮化硅双层切趾型 光栅的设计,需要优化的参数很多,参数包括硅层和氮化硅层的刻蚀槽宽,光栅 周期以及硅层中的亚波长光栅结构的占空比。仿真优化以 SiN-1 的氮化硅层结构, 硅层亚波长结构占据前8个光栅刻蚀槽的结构设计作为示例阐述,其他结构参数 以及类似结构设计,以相同的优化过程进行。从双层均匀结构出发,对双层光栅 设计进行优化。利用粒子群优化,仿真氮化硅层光栅占空比和周期长度以及硅层 光栅占空比和周期长度,得到双层均匀光栅仿真设计。在仿真过程中,将硅层光 栅划分为两个区域进行优化,在靠近 taper 区域的前端光栅周期长度为 501nm, 后端光栅周期长度为 532nm, 硅层光栅占空比 0.6, 氮化硅层刻蚀槽宽度 250nm, 氮化硅层光栅周期长度 600nm 时得到硅-氮化硅双层均匀光栅在 1310nm 波长处 的耦合效率为69%。在均匀结构的仿真设计基础上,引入切趾对双层光栅的结构 参数进行进一步的优化。首先对该结构进行双层线性切趾,也就是在硅层和氮化 硅层,同时引入线性切趾关系来定义硅层和氮化硅层沿 taper 指向光栅耦合区域 的占空比变化。此时, 硅层的线性切趾变化参数为 0.0125963, 氮化硅层的线性 切趾变化参数为 0.0125963, 两层的起始占空比均为 0.2, 在硅层光栅相对氮化硅 层光栅位移 2.52 μm 时, 光栅耦合器的仿真耦合效率为 72.48% (-1.4dB)。在这一 仿真结果上,继续对双层光栅的周期长度和刻蚀槽宽度分别在不同层的最小线宽 限制条件下,通过 FDTD 的 sweep 进行参数迭代扫描进行进一步切趾仿真优化。。

由于氮化硅层在靠近 taper 区域,需要更为准确的切趾优化来有效补偿光栅初端位置的模场失配损耗,因此在 taper 区域靠近光栅的上端,需要 2-5 个额外的氮化硅光栅结构,完成对整体损耗的进一步优化。最终得到该结构设计条件下的光栅仿真传输曲线如图 5.7 所示。

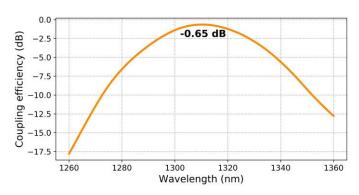

图 5.7 硅-氮化硅 (SiN-1) 双层切趾光栅仿真传输曲线

2D-FDTD 仿真得到的光栅在1310nm 中心波长时,峰值耦合效率为-0.65dB。将相应设计结果,通过第四章中的亚波长结构分析方法,就能将2D 仿真亚波长光栅所在刻蚀槽的等效折射率介质转换为相应的3D 结构中的实际亚波长光栅结构。最终在3D-FDTD 仿真中,得到1310nm 波长的耦合效率为-0.89dB。得到的仿真结构在3D-FDTD 条件下,同样具有较高的耦合效率,验证了结构设计的可行性。另外的氮化硅层条件与其他硅层设计的仿真结果在表5.2 中进行汇总。

| 设计编号 | SWG  | 氮化硅层 | SiN层最小线宽                       | Si层最小线宽  | Si层结构            | <b>2D</b> 仿真耦合效<br>  率 | 3D仿真耦合效<br>率 |

|------|------|------|--------------------------------|----------|------------------|------------------------|--------------|

| G1   | 前8周期 | SiN1 | SiN 250nm<br>SiN 最小间距<br>350nm | Si 140nm | 130nm单刻蚀<br>+SWG | -0.65dB                | -0.89dB      |

| G2   | 前8周期 | SiN2 | SiN 250nm<br>SiN 最小间距<br>350nm | Si 140nm | 130nm单刻蚀<br>+SWG | -0.76dB                |              |

| G3   | 前8周期 | SiN3 | SiN 250nm<br>SiN 最小间距<br>350nm | Si 140nm | 130nm单刻蚀<br>+SWG | -0.76dB                | -0.86dB      |

| G4   | 前9周期 | SiN1 | SiN 250nm<br>SiN 最小间距<br>350nm | Si 140nm | 130nm单刻蚀<br>+SWG | -0.83dB                |              |

| G5   | 前9周期 | SiN2 | SiN 250nm<br>SiN 最小间距<br>350nm | Si 140nm | 130nm单刻蚀<br>+SWG | -0.88dB                |              |

| G6   | 前8周期 | SiN3 | SiN 250nm<br>SiN 最小间距<br>350nm | Si 140nm | 130nm单刻蚀<br>+SWG | -0.69dB                |              |

| G7   | 前5周期 | SiN1 | SiN 250nm<br>SiN 最小间距<br>350nm | Si 140nm | 70/130nm双刻<br>蚀  | -1.03dB                |              |

|      |      |      |                                |          |                  |                        |              |

Si 140nm

70/130nm双刻

-1.15dB

-1.26dB

SiN 250nm

SiN 最小间距

表 5.2 硅-氮化硅双层切趾型光栅设计及相应仿真结果

G8

前5周期

SiN2

其中, 氮化硅层的最小线宽依据 AMF 工艺的制作水平进行仿真设置, SWG 在表中表示光栅设计中 SWG 占据光栅刻蚀槽的数量, 硅层结构沿用前面的分析 继续使用 140nm 作为最小线宽。对于 3D-FDTD 仿真验证,因为 G1,G2 与 G6 的硅层设计结构相同,只是氮化硅参数略有区别,所以只是在 G1 条件下进行了 3D-FDTD 仿真验证。其他 3D 仿真验证同理,只选取同类中的一组设计进行仿真 验证。2D-FDTD 与 3D-FDTD 在表 5.2 的设计中,最大偏差为 0.24dB,所以 2D-FDTD 仿真能够有效反应设计结构的耦合效率结果。得到的光栅 G2, G5 和 G8 在 SiN-2 结构参数下, 仿真峰值耦合效率分别为-0.76dB, -0.88dB 和-1.15dB: G4, G7 在 SiN-1 结构参数下, 仿真峰值耦合效率分别为-0.83dB 和-1.03dB; G3 和 G6 在 SiN-3 结构参数下,分别取得了-0.76dB 和-0.69dB 的耦合效率结果。通过对比 可以看出, 氮化硅结构参数仍旧会对仿真结构有一定的影响, 这主要是由于氮化 硅层的最小线宽较大,导致无法在不同氮化硅结构参数下的全部耦合区域做到最 优的切趾设计, 从而造成在不同的结构参数下有一定的耦合效率性能之差, 但是 本节中的设计结果均优于 5.2.2 节中的设计。G7 和 G8 设计因为 SWG 结构区域 较少,在硅层的 70/130nm 双刻蚀结合亚波长光栅设计中会带来相对较高的泄露 损耗, 故仿真结果也会比其他设计略低。

在实际制作过程中,氮化硅层结构会受到工艺误差产生一定的器件性能劣化。 考虑到工艺误差对光栅设计带来的影响,对光栅设计的氮化硅相关工艺容差进行 仿真。以硅-氮化硅(SiN-1)的 G1 光栅作为设计结构,仿真由淀积生长过程中 带来的氮化硅层厚度误差,氮化硅层到硅层间距误差以及后续氮化硅层结构光刻 对准时氮化硅层和硅层的层间对准误差的影响。验证设计器件对于工艺的敏感度, 仿真结果如图 5.8 中所示。

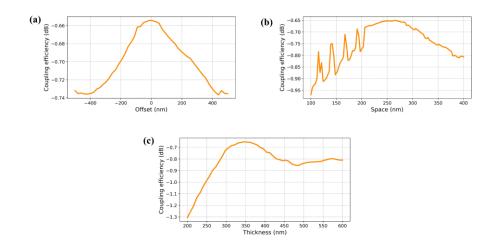

图 5.8 硅-氮化硅双层切趾光栅工艺容差仿真。(a) 硅-氮化硅层间对准误差仿真。(b) 硅-氮化硅间距误差仿真。(c) 氮化硅层厚度误差仿真。

在图 5.8 (a) 中,仿真±500nm 的氮化硅和硅层的层间对准误差对光栅耦合效率的影响。在这一误差范围内,对准误差带来光栅耦合器的额外损耗小于 0.1dB。图 5.8 (b) 展示了硅层到氮化硅层间距误差对光栅器件耦合效率的影响,在层间间距变化±150nm 时,额外损耗小于 0.4dB。同时可以看出,当层间间距增加时对性能影响较小,间距减小时会出现多个谐振峰的形式,这是由于处于不同间距条件下,部分区域的氮化硅光栅由于切趾设计,在相应厚度下也能满足增透膜设计条件造成的。图 5.8 (c) 仿真了氮化硅层厚度变化±200nm 对光栅耦合效率的影响,在这一仿真误差下,光栅的额外损耗小于 0.7dB。通过三种工艺条件的仿真,设计的光栅具有较高的氮化硅相关工艺容差。

# 5.2.5 硅-氮化硅双层切趾光栅测试结果

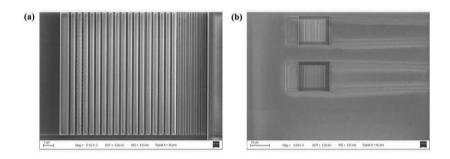

根据初次设计的硅-氮化硅参数,在新加坡 AMF 公司进行硅-氮化硅光栅设计的样品试制工作。具体氮化硅参数采用 5.2.1 节中的氮化硅参数进行制作,得到的器件 SEM 结果如图 5.9 所示。

图 5.9 硅-氮化硅双层光栅 SEM 结果。(a) 光栅结构细节 SEM 图。(b) 光栅结构缩略 SEM 图。

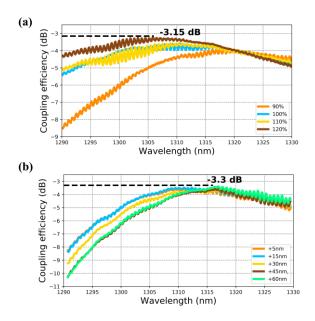

图 5.9 是制造得到的硅-氮化硅双层光栅器件的 SEM 结果。对得到的光栅样品进行测试,测试得到 AMF 工艺制作下光栅器件的传输曲线。与 5.2.3 节中进行相同的实验设置,设置实验组对硅层光栅的刻蚀槽宽度和亚波长结构的刻蚀槽宽度同时进行线宽比例补偿,补偿相应工艺线宽误差的影响。而同时,还对部分光栅设置硅-氮化硅对准误差补偿实验组,该实验组通过在版图中额外引入硅-氮化硅层间的对准误差,用于补偿实际制作过程中该误差的影响。其中得到的最优测试结果为 G7(硅层 70/130nm 双刻蚀亚波长光栅,氮化硅 SiN-1 参数)和 G8(硅层 70/130nm 双刻蚀亚波长光栅,氮化硅 SiN-2 参数)光栅设计的传输曲线,如图 5.10 所示。

图 5.10 硅层双刻蚀结构的硅-氮化硅双层光栅设计测试结果。(a) G7 光栅整体 结构比例补偿组。(b) G8 光栅硅-氮化硅对准误差补偿组。

在图 5.10 (a) 中,展示了 G7 光栅在硅层线宽补偿实验组中得到的测试传输 曲线结果。在刻蚀槽宽 120%补偿组下,得到 1306nm 波长处的峰值耦合效率为-3.15dB。在刻蚀槽宽度 100%和 110%补偿组中,测试峰值耦合效率为-3.5dB。在 刻蚀槽宽度 90%补偿组条件下,测试峰值耦合效率仅为-3.9dB。图 5.10 (b) 是 G8 光栅在硅-氮化硅层间对准误差实验组中得到的测试数据, 在层间对准误差为 +60nm 时,得到 1316nm 波长处,测试峰值耦合效率为-3.3dB。该对准误差的定 义与 C 波段实验结果中的对准误差方向相同,+方向表示远离 taper 区域的方向。 测试结果由于在 AMF 制作中, SWG 区域的滞后效应和实际氮化硅制作线宽未 达到设计所需的最小线宽问题,导致其他设计的测试结果比这两种结果更低,而 这两种结果也未体现出优于本文其他设计的测试耦合效率。具体到实验测试组中, 可以发现图(a)的设计在刻蚀槽宽120%补偿组中比不进行补偿的设计组耦合效 率高出 0.45dB, 同时, 随着线宽补偿比例的增加, 峰值耦合效率也不断提升。与 硅光栅在 AMF 测试得到的结果对比可知, AMF 在硅层的线宽不会发生达到 120% 的制作误差, 硅光栅的设计均在硅层不补偿时取得最优值。因此, 可以对比两个 结果推知是当前结构的亚波长滞后效应以及氮化硅层结构参数导致的耦合效率 下降。在图(b)的设计中,硅-氮化硅对准误差在+5nm~+30nm 范围内变化时, 光栅中心波长基本不变,峰值耦合效率在 3.4dB~3.6dB 的范围内变化。而随着对 准误差增加到+45nm 和+60nm 时,中心波长发生偏移,同时峰值耦合效率也得到 提升。这一结果说明当前氮化硅层结构参数与仿真预期不符,在发生较大硅-氮 化硅层对准误差时反而具有 0.1~0.3dB 的耦合效率提升。

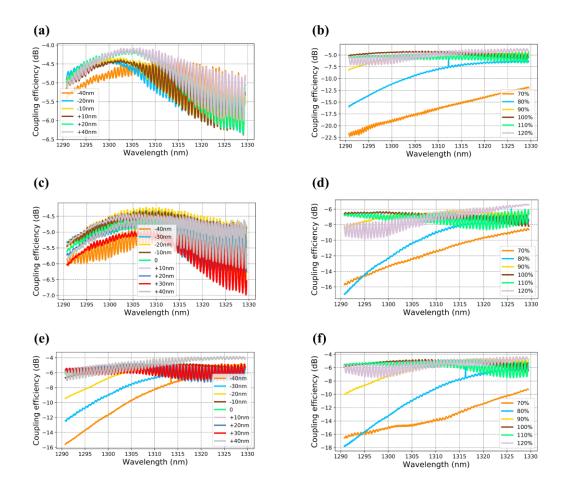

对得到的 G1-G3 硅层 130nm 单刻蚀+8 周期 SWG 结构的硅-氮化硅双层光栅实验组测试结果进行分析,得到的器件测试结果如图 5.11 所示。得到的结果中,图 (a)-图 (c)为 SiN-1参数条件的双层光栅实验测试结果。图 (a)是硅-氮化硅对准误差补偿实验组,同样是通过在硅和氮化硅两层之间的版图中,额外引入的位移偏差,补偿制作过程中对准误差带来的工艺影响。对准误差的正方向同样表示为从 taper 区域指向光栅耦合区域。得到在+40nm 对准误差补偿条件下,1305nm 中心波长的峰值耦合效率为-4.1dB。在+20nm 对准误差补偿时,峰值测试耦合效率为-4.2dB。而随着对准误差补偿组的补偿数值向负方向偏移,峰值测试耦合效率逐渐降低。在-10nm,+10nm,-20nm,-40nm 条件下,得到测试

峰值耦合效率在不同中心波长下均为-4.4dB。图(b)则是对硅层整体刻蚀槽宽以 及亚波长光栅区域的垂直光传播方向的刻蚀槽宽进行比例补偿,得到在120%比 例补偿时, 1324nm 中心波长的测试耦合效率为-3.4dB。在 70%, 80%, 90%, 100%, 110%线宽补偿组中, 分别测得峰值耦合效率为-12dB, -5.9dB, -4.5dB, -4.2dB, -4.3dB。图(c)则是对硅层整体刻蚀槽宽度的定值补偿,得到在+40nm 线宽定值补偿条件下, 1329nm 中心波长处的测试耦合效率为-3.8dB。在线宽定 值补偿为-40nm, -30nm, -20nm, -10nm, 0, +10nm, +20nm, +30nm 时, 测试 峰值耦合效率分别为-5.4dB, -4.5dB, -4.5dB, -4.5dB, -5.0dB, -4.3dB。 图 (d) 则是 SiN-3 参数条件下的 G2 设计光栅实验结果, 在硅层刻蚀槽宽度和亚 波长刻蚀槽宽度比例补偿 120%时,得到同组最优测试结果为-5.5dB。这一结果 主要是由于 SiN-3 层厚度最厚,相比其他设计而言,其氮化硅层最小线宽更难达 到设计值,产生了更大的仿真-实验偏差。本组测试结果中其他结果比最优测试 结果相对更差,参考意义不大。图(e)和图(f)则分别是SiN-2参数条件下的 G3 设计的硅层整体结构定值补偿组和比例补偿组,实验最优值同样出现在 +40nm 和 120%线宽补偿组, (e) 图中在 1324nm 中心波长的测试耦合效率为-3.8dB; (f) 图中在 1327nm 中心波长的测试耦合效率为-4.2dB。在定值补偿组的 -40nm, -30nm, -20nm, -10nm, 0, +10nm, +20nm, +30nm 条件下, 测试峰值 耦合效率为分别为-5.5dB,-5.1dB,-4.8dB,-4.7dB,-4.5dB,-4.8dB,-4.9dB,-4.7dB。在比例补偿组 70%, 80%, 90%, 100%, 110%条件下, 测试峰值耦合效 率则分别取-9.0dB, -5.8dB, -4.7dB, -4.8dB, -4.8dB。G1-G3 的结果由于亚波长 结构相较于 G7 和 G8 设计较多, 受到滞后效应影响更为严重, 因此得到的结果 中测试耦合效率相比 G7 和 G8 设计更低。通过对比两组实验可知, G1 光栅与 G7 光栅氮化硅结构参数相同,二者设计的不同在于硅层的结构设计,G7 光栅亚 波长光栅所在刻蚀槽为5个,比G1光栅的8个更少,相应受到亚波长光栅滞后 效应的影响更小。而实验结果中, G7 光栅最优测试耦合效率为-3.15dB, 高于 G8 光栅-3.4dB 的最优测试损耗。验证了滞后效应对整体设计产生影响的分析。

图 5.11 硅层 8 周期 SWG 结构硅-氮化硅双层光栅测试结果。SiN-1 参数 G1 光栅设计 (a) 硅-氮化硅对准误差补偿实验组。(b) 硅层整体结构比例补偿组。(c) 硅层光栅刻蚀槽宽定值补偿组。SiN-3 参数 G2 光栅设计 (d) 硅层整体结构比例补偿组。 SiN-2 参数 G3 光栅设计 (e) 硅层整体结构定值补偿组。(f) 硅层整体结构比例补偿组。

图 5.12 硅层 9 周期 SWG 结构硅-氮化硅双层光栅设计测试结果。SiN-3 参数 G4 光栅设计 (a) 硅-氮化硅对准误差补偿组和 (b) 硅层整体结构定值补偿组。SiN-1 参数 G5 光栅设计 (c) 硅层整体结构比例补偿组。SiN-2 参数 G6 光栅设计 (d) 硅层整体结构比例补偿组。

对硅层 9 周期 SWG 结构的硅-氮化硅双层光栅 G4-G6 测试结果同样进行分析,得到的测试结果如图 5.12 所示。在图 5.12 中,图 (a) 和图 (b) 是在 SiN-3 结构参数下的双层光栅测试结果,(a) 为硅-氮化硅对准误差补偿组,在-10nm补偿条件下,在 1302nm 中心波长的测试峰值耦合效率为-8.9dB。(b) 则是硅层刻蚀槽宽度和决定亚波长区域等效有效折射率的横向刻蚀槽宽度的整体定值补偿实验组,得到+20nm 线宽补偿实验下,测试在 1327nm 波长处的峰值耦合效率为-9.2dB。这两组结果相较于之前的测试结果,进一步验证了 SiN-3 参数未达到设计线宽的问题,测试耦合效率恶化较多,仅获得 9dB 附近的测试结果。此外,由于亚波长结构数量的进一步增加,相比 G2 的设计结果也证明了耦合效率的恶化与亚波长结构数量直接相关,印证了前文中滞后效应影响的分析,在相同 SiN-3 参数条件下,SWG 结构 8 周期设计最优测试损耗为-5.5dB,相比之下其他结构参数相同,SWG 周期的增加使得耦合效率进一步恶化到-9.0dB。图 (c) 是在 SiN-1 氮化硅参数条件下的测试结果,在硅层整体刻蚀槽宽度(包括垂直光传播方向的亚波长结构刻蚀槽)比例补偿实验组中,120%线宽补偿组得到 1306nm 中心波长的-5.0dB 的测试耦合效率结果。在比例补偿 70%,80%,90%,100%,110%

条件下,测试峰值耦合效率分别为-13.5dB, -8.5dB, -7.5dB, -5.8dB, -5.8dB。图 (d)是在SiN-2参数下的硅层整体刻蚀槽宽度比例补偿组测试结果,同样在120%线宽比例补偿组中得到同组最优测试值,1305nm 中心波长处的峰值耦合效率为-4.0dB。在比例补偿70%,80%,90%,100%,110%条件下,测试峰值耦合效率分别为-15dB,-9.0dB,-6.0dB,-6.0dB,-6.0dB。在相同的硅层结构设计中也可以看出,SiN-2 由于其氮化硅层厚度最薄,得到的每组测试结果中,实验结果最优。具体到实验组中,在硅层单刻蚀+9 周期 SWG 结构下,SiN-2 相较于 SiN-1参数的设计耦合效率提升 1dB,相较于 SiN-3 参数的设计提升更多,而氮化硅层的厚度与氮化硅层设计的最小线宽直接相关。因此,考虑这是由于制作过程中,SiN-2 层的氮化硅最小线宽最为接近设计值,随着氮化硅层厚度的增加,实际制作结果逐渐偏离最优值以及实际仿真过程中本身存在的一定耦合效率差造成不同氮化硅层设计之间偏差的结果。

#### 5.3 硅-氮化硅优化参数光栅耦合器

在 5.2 节的仿真和制作中,可以看出氮化硅层在实际工艺中的最小线宽制作能力以及滞后效应的问题,均对最终的实验结果有较大的影响。基于这两点考虑本节在 5.2 节的基础上,通过与组内合作得到后续流片的优化氮化硅参数,进行对后续 AMF 流片工艺的硅-氮化硅光栅的设计工作。

# 5.3.1 氮化硅优化参数的确定

在 5.2 节中完成对应于氮化硅层参数的光栅耦合器设计后,于后续的 AMF 流片工艺继续进行讨论。主要讨论对于氮化硅层结构最小线宽限制的减小以及整体晶圆上包层二氧化硅厚度的问题。在图 5.3 的氮化硅参数条件下,由于两层氮化硅层厚度分别为 350nm 和 400nm,而氮化硅层的刻蚀配方以及刻蚀过程中的掩膜刻蚀比,会在最小线宽与氮化硅层厚度之间形成一个接近于 1:2 的关系<sup>[66]</sup>。因此,在 5.2.1 节的参数条件下,仅有 200nm 厚度的氮化硅层有实现氮化硅层更小线宽结构的可能。但是 200nm 厚度的氮化硅是由 350nm 厚度的氮化硅基础上刻蚀形成,后续没有加入更高精度的光刻工艺,所有设计的最小线宽均较大。为减小最小线宽的限制条件,通过组内与 AMF 进行沟通讨论,最终得出在氮化硅

厚度较小时,可以制作较小线宽的氮化硅层器件。在后续的 AMF 流片中,保留最上层的 400nm 氮化硅,用于实现低损耗的交叉设计及低损耗氮化硅波导,下层氮化硅优化为较小厚度的氮化硅层结构参数。与此同时,模斑转换器需要较厚的上包层实现对光模场沿芯片法线方向的有效扩展。对于光栅器件而言,上包层相当于一系列的介质层组合,设计好的光栅在一系列的介质层的建设性干涉条件下实现高耦合效率输出/输入。但是随着介质层厚度的增加,总会在额外增加的介质层上带来一定的泄露损耗问题。这种泄露损耗的叠加,不可避免引起最终的耦合效率降低。故对光栅器件,需要较薄上包层厚度的工艺条件实现更低损耗设计。通过与组内同学合作讨论,最终确定后续氮化硅工艺的 AMF 流片参数,如图 5.13 所示。

图 5.13 优化后的氮化硅层结构参数示意图

在图 5.13 的光栅区域处,通过将光栅层的区域的顶部上包层刻蚀工艺,实现对光栅器件性能的优化。而下层氮化硅 SiN-4 层由于厚度只有 250nm,所以该氮化硅层的最小线宽可以考虑进行 140nm 的试制工作。此时 SiN-4 距离顶层硅的间距为 350nm,SiN-4 层氮化硅的厚度为 250nm;SiN-5 距离顶层硅的间距为 950nm,厚度为 400nm。

# 5.3.2 硅-氮化硅双层光栅耦合器设计

在这一优化后的氮化硅层结构参数下,继续对不同氮化硅工艺条件的硅-氮化硅多层光栅设计进行优化仿真。仿真过程与前述 5.2 节的过程相同,在设计上为保证尽可能排除滞后效应的影响,增加了无硅层亚波长光栅结构的多层光栅设计。同时,在具有亚波长光栅的设计中,增加考虑第四章滞后效应影响的光栅仿

真,进一步消除仿真和制造过程中带来的性能偏差问题。此外,由于实际和 AMF 沟通中,工艺制作的氮化硅层光栅的最小线宽相较于普通器件具有更为严格的制 作要求,代工厂给出的光栅刻蚀槽间距比线宽最小线宽更大。在实际的最小线宽 要求中,光栅刻蚀槽宽度的最小线宽比光栅齿最小线宽大 50-100nm。故在部分 设计中,调整氮化硅层最小线宽的限制,以保证得到稳定的制造结果。在实际设 计过程中,根据氮化硅层厚度的不同,依据 AMF 代工厂给出的工艺制作能力, 设置 SiN-4 层采用 150nm 最小光栅齿宽度, 200nm 最小刻蚀槽宽度; SiN-5 层采 用 250nm 最小光栅齿宽度, 350nm 最小刻蚀槽宽度。首先在工艺优化的上包层 刻蚀条件下,对O波段,上包层 1.41 um 结构的光栅进行仿真设计,在平头光纤 测试条件下进行仿真模拟。仿真同样以第四章中的设计作为硅层结构基础,采用 硅层双刻蚀结构以及硅层 130nm 单刻蚀+SWG 结构进行仿真。在此基础上,通 过引入相应氮化硅层参数,得到在不同氮化硅参数以及硅层结构条件下的仿真设 计结果。仿真从第四章中的结构出发,首先优化氮化硅层结构参数,得到氮化硅 层在相应双层光栅结构下的最优氮化硅层光栅周期和占空比。随后,对整体结构 的不同层刻蚀槽宽度和周期进行 FDTD 中的 sweep 迭代扫描优化。由于氮化硅 层在实际设计过程中,被设计作为增透膜结构,对于光栅最终耦合效率的影响相 对硅层设计较低。因此,在切趾优化过程中,通过从硅层优化到氮化硅层的顺序 进行, 最终设计结果如表 5.3 所示。最小线宽在表中表示为 CD, 间隔则是光栅 刻蚀槽的最小刻蚀槽宽度,耦合效率用 CE 表示。

表 5.3 上包层 1.41μm 的 O 波段光栅仿真设计结果

| 设计编号 | SWG  | SiN层结构      | SiN参数                | SiN层CD              | Si层结构            | 2D仿真CE   |

|------|------|-------------|----------------------|---------------------|------------------|----------|

| GC1  | 1    | 全刻蚀切趾光栅     | 950nm 间距<br>400nm 厚度 | 250nm CD<br>350nm间隔 | 70/130nm双刻蚀      | -1.25 dB |

| GC2  | 1    | 全刻蚀<br>切趾光栅 | 350nm 间距<br>250nm 厚度 | 250nm CD<br>350nm间隔 | 70/130nm双刻蚀      | -0.99 dB |

| GC3  | 前9周期 | 全刻蚀 切趾光栅    | 350nm 间距<br>250nm 厚度 | 150nm CD<br>200nm间隔 | 130nm单刻蚀<br>+SWG | -0.7 dB  |

得到的光栅设计 GC2 在无 SWG 条件, SiN-4 条件下, 能够实现-0.99dB 的 仿真结果, 具有较强的工艺可实现性和仿真性能。GC3 在硅层的 SWG 设计及 SiN-4 条件下, 具有-0.7dB 的仿真耦合效率。而 GC1 光栅在双刻蚀硅层结构设计

下,由于氮化硅层结构参数的厚度在当前结构下对光栅耦合效率的影响作用较低,同样相较于硅层光栅设计出现了对耦合效率一定程度的降低。未取得明显的优化结果。

在考虑到第四章中滞后效应影响后,增加对本节前述内容中仿真效果较好的 双层光栅设计。结合第四章中的实验结果,将亚波长光栅所在区域的刻蚀深度降 低,在亚波长区域考虑滞后效应影响后,在不同设计中得到的结果如表 5.5 所示。

| 设计编号 | SWG  | SiN层结构      | SiN参数                | SiN层CD              | Si层结构            | 2D仿真CE   | 上包层厚度  |

|------|------|-------------|----------------------|---------------------|------------------|----------|--------|

| GC10 | 前9周期 | 全刻蚀<br>切趾光栅 | 350nm 问距<br>250nm 厚度 | 150nm CD<br>200nm间隔 | 130nm单刻蚀<br>+SWG | -1.23 dB | 3 μm   |

| GC11 | 前9周期 | 全刻蚀<br>切趾光栅 | 350nm 间距<br>250nm 厚度 | 350nm CD<br>350nm间隔 | 130nm单刻蚀<br>+SWG | -1.0 dB  | 3 μm   |

| GC12 | 前9周期 | 全刻蚀<br>切趾光栅 | 350nm 间距<br>250nm 厚度 | 150nm CD<br>200nm问隔 | 130nm单刻蚀<br>+SWG | -0.74 dB | 1.4 μm |

| GC13 | 前9周期 | 全刻蚀<br>切趾光栅 | 350nm 间距<br>250nm 厚度 | 350nm CD<br>350nm间隔 | 130nm单刻蚀<br>+SWG | -0.75 dB | 1.4 μm |

表 5.5 考虑滞后效应的亚波长光栅设计仿真结果

设计得到的光栅结果中,同样出现由于更大线宽的氮化硅层设计建立在之前小线宽设计的基础上进行优化,在大线宽条件下表现出更优的设计结果的现象。GC11的仿真峰值耦合效率为-1.0dB,高于 GC10的-1.23dB;而 GC12与 GC13的-0.74dB和-0.75dB基本相同。两组控制其他参数不变,仅对比上包层厚度的不同能够发现,同样存在之前分析的较薄上包层条件对于光栅耦合效率的优化现象。

### 5.3.3 硅-氮化硅多层光栅耦合器设计

在优化后的硅-氮化硅参数的双层光栅设计基础上,因为有两层不同结构参数的氮化硅可供设计,所以考虑在设计时同时结合两层氮化硅结构,本节提出硅-氮化硅-氮化硅三层光栅耦合器设计。该设计主要考虑在已有的双层设计基础上,进一步通过双层氮化硅的切趾结构,实现对不同光栅耦合器区域内模场失配损耗的继续降低。也就是在5.3.2设计的基础上,多引入一层氮化硅光栅,进一步在光栅的不同区域内,实现更优的切趾设计效果;与此同时,两层氮化硅层经过设计,同时作为增透膜结构作用,也有实现耦合效率进一步提升的潜力。

设计过程以及整体设计参数与前述章节的双层切趾型光栅相似,不同的设计在于三层光栅同时进行切趾优化,得到不同结构参数下的相应设计结果。三层光栅的设计以双层光栅中仿真结果较高的设计作为优化起点,通过在双层光栅结构基础上,对三层可优化的结构参数进行切趾优化,得到不同结构设计条件下的仿真优化结果。在三层光栅耦合器的设计中,考虑将额外增加的一层氮化硅不进行刻蚀,只作为一定厚度和间距的增透膜结构,也进行了部分设计的仿真。这种结构的优点相较于三层切趾光栅的结构来说,能够相对三层光栅设计简化工艺难度,提高工艺容差,无需考虑三层结构的对准问题,仅在有光栅结构的两层需要进行层间对准问题分析。得到的仿真结果如表 5.7 中所示。表中的 space1 表示上层氮化硅到硅层的间距,th1 和 th 则分别表示上层氮化硅厚度和下层氮化硅厚度。在表中的最小线宽,仅有一组线宽说明的表示上下层氮化硅线宽均满足相应的条件,CD1 和间隔 1 则表示最上层氮化硅的最小线宽和最小刻蚀槽宽度。

表 5.7 得到的仿真结果中, 滞后效应 TG7 和 TG8 表示考虑滞后效应影响的 三层光栅仿真设计结果, 仿真分别得到的耦合效率为-0.66dB 和-0.85dB。FA 测 试 TG9, TG10 和 TG11 则代表光纤阵列测试条件的三种三层光栅设计的仿真结 果, 最终得到的仿真耦合效率结果分别是-1.21dB, -1.2dB 和-0.79dB。TG1-TG6 则是平头光纤测试条件下,不考虑滞后效应影响的仿真结果。TG1,TG2,TG5 和 TG6 设计均是三层光栅切趾设计结果,得到最优设计为 TG5 的-0.66dB,该设 计的硅层结构为 130nm 单刻蚀 8 周期 SWG 结构, 氮化硅层则同时在 140nm 最 小线宽下完成两层氮化硅的光栅切趾,得到最终的 TG5 设计。TG1 和 TG2 则分 别得到-0.98dB 和-1.07dB 的仿真耦合效率。TG3 和 TG4 则是在顶层氮化硅不进 行刻蚀条件下的三层设计,得到在无 SWG 结构辅助下,TG3 的耦合效率为-1.03dB, TG3 设计在硅层采用 70/130nm 双刻蚀切趾结构, 顶层氮化硅不进行刻 蚀,下层氮化硅在 140nm 最小线宽下切趾,实现的相应光栅设计。虽然仅从仿 真结果来看,使用光纤阵列测试条件的仿真结果未表现出相较于平头光纤条件明 显的优势,但是在实际测试过程中,光纤阵列的测试形式,既可以有效贴合封装 时的应用,降低封装过程中引入的额外损耗;又可以在实际测试中降低空气及测 试环境杂质的影响。具有一定的设计意义。而三层光栅耦合器整体相对于双层光 栅设计来说,未表现出明显的优化结果,该仿真结果也表明,在优化参数进一步

增加的设计中,现行优化方法均出现难以搜索到最优值的问题,有待进一步解决探索。

表 5.7 硅-氮化硅-氮化硅三层光栅设计仿真结果

| 设计编号         | SWG  | 氮化硅<br>层                                | SiN层结构参数                                                           | SiN层最小线<br>宽                                 | Si层结构            | 上包层厚度   | 2D仿真耦<br>合效率 |

|--------------|------|-----------------------------------------|--------------------------------------------------------------------|----------------------------------------------|------------------|---------|--------------|

| TG1          | 前8周期 | 双层SiN<br>切趾GC                           | 350nm space<br>250nm th<br>950nm space1<br>400nm th1               | 150nm CD<br>200nm间隔<br>250nm CD1<br>350nm间隔1 | 130nm单刻<br>蚀+SWG | 3 μm    | -0.98dB      |

| TG2          | 前8周期 | 双层SiN<br>切趾GC                           | 350nm space<br>250nm th<br>950nm space1<br>400nm th1               | 350nm CD<br>350nm间隔<br>250nm CD1<br>350nm间隔1 | 130nm单刻<br>蚀+SWG | 3 μm    | -1.07dB      |

| TG3          | 无    | Middle<br>SiN 全刻<br>蚀<br>TOP SiN<br>不刻蚀 | 350nm space<br>250nm th<br>950nm space1<br>400nm th1               | 140nm                                        | 70/130nm双<br>刻蚀  | 3 μm    | -1.03dB      |

| TG4          | 无    | Middle<br>SiN 全刻<br>蚀<br>TOP SiN<br>不刻蚀 | 350nm space<br>250nm th<br>950nm space1<br>400nm th1               | 350nm CD<br>350nm间隔<br>350nm CD1<br>350nm间隔1 | 70/130nm双<br>刻蚀  | 3 μm    | -1.34dB      |

| TG5          | 前8周期 | 双层SiN<br>切趾GC                           | 350nm space<br>250nm th<br>950nm space1<br>400nm th1               | 140nm                                        | 130nm单刻<br>蚀+SWG | 1.41 μm | -0.66dB      |

| TG6          | 无    | 双层SiN<br>切趾GC                           | 350nm space<br>250nm th<br>950nm space1<br>400nm th1               | 140nm                                        | 70/130nm双<br>刻蚀  | 1.41 μm | -0.99dB      |

| 滞后效应<br>TG7  | 前8周期 | 双层SiN<br>切趾GC                           | 350nm space<br>250nm th<br>950nm space1<br>400nm th1               | 140nm                                        | 130nm单刻<br>蚀+SWG | 1.41 μm | -0.66dB      |

| 滞后效应<br>TG8  | 前8周期 | 双层SiN<br>切趾GC                           | 350nm space<br>250nm th<br>950nm space1<br>400nm th1               | 350nm CD<br>350nm间隔<br>350nm CD1<br>350nm间隔1 | 130nm单刻<br>蚀+SWG | 3 μm    | -0.85dB      |

| FA测试<br>TG9  | 前8周期 | 上层SiN<br>不刻蚀<br>下层SiN<br>全刻蚀            | 950nm space<br>400nm thickness<br>350nm space1<br>250nm thickness1 | 150nm CD<br>200nm间隔<br>250nm CD1<br>350nm间隔1 | 130nm单刻<br>蚀+SWG | 5 μm    | -1.21dB      |

| FA测试<br>TG10 | 前8周期 | 双层全刻<br>蚀切趾光<br>栅                       | 950nm space<br>400nm thickness<br>350nm space1<br>250nm thickness1 | 150nm CD<br>200nm间隔<br>250nm CD1<br>350nm间隔1 | 130nm单刻<br>蚀+SWG | 5 μm    | -1.2dB       |

| FA测试<br>TG11 | 前8周期 | 双层全刻 蚀切趾光 栅                             | 950nm space<br>400nm thickness<br>350nm space1<br>250nm thickness1 | 150nm CD<br>200nm间隔<br>250nm CD1<br>350nm间隔1 | 130nm单刻<br>蚀+SWG | 5 μm    | -0.79dB      |

### 5.4 本章小结

本章在硅光栅耦合器设计的基础上,通过引入多层氮化硅结构,提出了一种 高效宽带光栅耦合器设计,该设计能够有效兼容氮化硅材料的带宽特性以及在垂

直方向上利用多层结构实现耦合效率的提升。在 AMF 流片工艺条件下,结合组内同学一起讨论得到的氮化硅工艺参数,设计了硅-氮化硅双层光栅耦合器设计,仿真得到的耦合效率最优值为-0.65dB。在实验中证明了硅层作为传输层的 O 波段硅-氮化硅双层光栅耦合器设计,得到最优测试结果为-3.15dB。后续在第一次氮化硅层参数设计基础上,根据氮化硅最小线宽制作问题,与组内同学合作讨论得到了优化后的氮化硅层参数。在优化氮化硅参数以及相应的线宽限制条件下,对硅-氮化硅双层光栅以及硅-氮化硅-氮化硅三层光栅进行设计。设计得到在硅氮化硅双层光栅中,仿真耦合效率最优值为-0.7dB。三层硅-氮化硅-氮化硅光栅的仿真耦合效率最优值为-0.66dB。 在优化后的氮化硅条件下,进行的相应多层光栅耦合器设计已经在新加坡 AMF 代工厂进行流片验证,目前流片结果尚未返回,所以 5.3 节中的设计暂未得到相应的测试结果。

#### 6 总结与展望

本文的工作以低损耗光栅耦合器设计作为主要内容,在 C 波段和 O 波段条件下分别开展设计,通过不同的设计结构,实现高耦合效率的仿真和测试结果。尽管本文中有一部分的光栅设计由于最后一次的 AMF 流片结果未完成制作,未得到相应的制作结果。本文还是取得了一些重要的成果,主要包括:

- 1. 提出了一种用于多参数光栅切趾优化的定向优化方法,通过对不同参数 加权排序,在多参数条件下快速得到仿真结果。在后续的光栅设计中,通过对不同光栅周期的权重分析,得到最优的不同结构参数仿真顺序。 降低因多参数应用中,很多需要优化的结构参数导致难以搜索到最优值的问题。在交错刻蚀切趾型光栅设计中,通过在相同仿真条件下进行对比,提出的定向优化方法相较于光栅优化常用的粒子群优化方法,能够在有限次迭代中,快速收敛到最优值。与此同时,在优化参数数量进一步增加时,能够在定向优化方法下,搜索得到优化设计结果。

- 2. 对于 C 波段 70nm/220nm 交错刻蚀硅光栅设计,在鲁棒性版图设计辅助 下,通过扩展后续 220nm 刻蚀工艺对应的光刻胶掩膜,实现对不同刻蚀 工艺间对准误差问题的补偿作用。通过结合交错刻蚀和切趾设计, 完成 C 波段交错刻蚀切趾型光栅设计, 仿真得到在 140nm 最小线宽条件下, 峰值耦合效率为-1.24dB。对设计的器件进行流片验证,测试得到 C 波段 下,峰值耦合效率为-2.2dB的交错刻蚀型光栅耦合器。据作者所知,该 结果为无其他介质层和 SWG 结构的 C 波段商用硅光工艺制作, 130nm CMOS 工艺节点的最低损耗硅光栅。在 C 波段铌酸锂光栅的设计中, 结 合实验室工艺条件, 在考虑实际制作过程中铌酸锂光栅刻蚀侧壁倾角及 制作中波导缩窄问题的影响,首次实验证明了灰度刻蚀结合切趾设计的 C 波段铌酸锂光栅, 通过对铌酸锂光栅结构参数的仿真设计, 得到铌酸 锂光栅在 500nm 最小线宽条件下,光栅的耦合效率为-3.7dB,与设计相 对应的测试得到最优峰值耦合效率为-7.1dB。同时,也设计了在 400nm 最小线宽条件下的铌酸锂光栅耦合器, 在切趾设计优化后, 得到光栅耦 合器的仿真耦合效率为-2.97dB。后续的设计由于时间关系未完成相应器 件的制作。

3. 仿真并实验证明了 130nm 单刻蚀的低损耗亚波长光栅设计,通过考虑滞后效应的影响以及对 EMT 的修正,仿真设计得到 130nm 单刻蚀的亚波长光栅耦合效率为-1.0dB,测试得到的峰值耦合效率为-1.93dB。在此基础上,提出了一种新型的渐变亚波长结构的概念,在梯形亚波长结构下实现亚波长结构所在刻蚀槽的折射率渐变,仿真得到 130nm 单刻蚀梯形亚波长光栅耦合效率为-0.83dB,测试得到的峰值耦合效率为-1.73dB。该测试结果为 O 波段无金属反射镜和底部分布式反射镜的世界最低损耗单刻蚀光栅。通过组内合作,确定流片工艺的氮化硅参数,在得到的氮化硅结构参数基础上,通过将氮化硅层设计作为增透膜结构,设计了硅-氮化硅增透膜结构光栅设计,通过 AMF 流片得到最优测试结果为-3.2dB。在这一设计基础上,考虑将氮化硅层设计为光栅的形式,实现对光栅的更优切趾设计和对氮化硅层折射率的调整,首次实验证明了以氮化硅为增透膜的硅-氮化硅双层切趾光栅,仿真得到 O 波段下,峰值耦合效率为-0.66dB。测试得到的最优峰值耦合效率为-3.15dB。

对整体文章中出现的问题进行总结,对后续工作进行一些进一步的展望:

- 1. 铌酸锂光栅耦合器由于灰度刻蚀区域整体长度较短,在较短的灰度刻蚀 区域实现较大的厚度变化时,在实际制作过程中,于灰度刻蚀结构上产 生较为明显的褶皱现象。该类光栅可以通过增加灰度刻蚀区域长度,获 得更优的测试结果。与此同时,通过更小线宽的铌酸锂仿真设计和制作, 可以实现更高耦合效率的铌酸锂光栅设计。通过在实验室工艺条件下进 行迭代优化,实现铌酸锂光栅耦合效率上的进一步提升。

- 2. 对 O 波段六边形和圆角梯形的新型亚波长光栅结构设计,仅完成了均匀结构的仿真设计和实验制作,后续可以在此基础上做进一步切趾优化,能够得到更高耦合效率的测试结果。此外,由于 70nm 刻蚀深度在引入切趾后,由于刻蚀深度较浅,会导致在光栅后端区域与光纤模场匹配过程中,带来一定的损耗。因此,可以考虑也在 130nm 的硅光工艺常用刻蚀深度,对六边形和圆角梯形结构的新型亚波长光栅进行设计,实现对光栅耦合效率上的进一步突破。